# 나노 SoC

- 1. 개요

- 1.1. 기술개요

- 1.1.1. 중점기술 및 표준화항목의 정의

- 중점기술의 정의

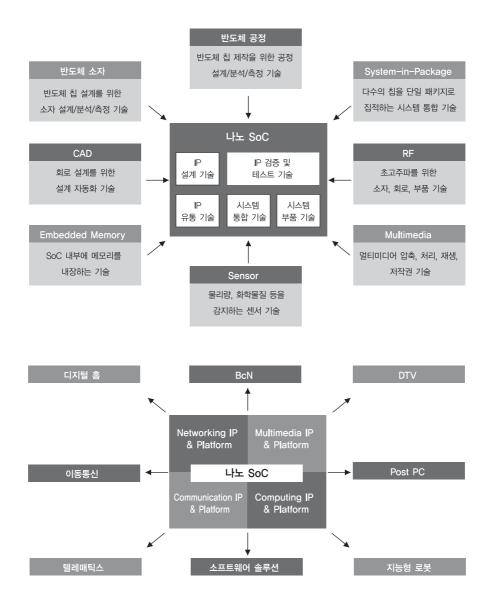

IP 기반 설계에 의하여 System-on-Chip과 관련 부품을 설계, 개발 및 구현하는 기술

- 나노 SoC는 대표적인 반도체 시스템인 System-on-Chip과 여기에 필요한 각종 부품을 설계, 개발 및 구현하는 기술

- System-on-Chip은 정보통신기기의 핵심기능을 처리하는 메모리, 디지털 회로, 아날로그 회로, CPU, 센서, 안테나, 수동 소자 등을 하나의 반도체 칩에 집적하는 기술

- IP는 동작이 검증되고 나노 SoC 설계에서 재사용이 가능한 설계 Block을 의미

- IP를 기반으로 SoC를 설계하는 방법에는 블록 기반 설계방법과 플랫폼 기반 설계 방식이 있음

- 블록 기반 설계는 시스템을 여러 블록으로 설계하고 필요로 하는 IP들은 기존의 IP를 재사용하거나 IP 공급 자로부터 구입하여 시스템을 구성하고 검증하는 방법

- 플랫폼 기반 설계는 공통적인 아키텍처와 중앙 프로세서에 상주하는 OS등 범용적인 플랫폼을 구성해 놓고 필요에 따라서 소프트웨어를 변경하거나 새로운 기능 블록을 추가하는 방법으로 시스템을 재구성하는 방법

### ○ 표준화항목의 정의

- 나노 SoC와 관련된 요소기술은 (1) 나노 SoC를 구현하는 기본 요소인 IP를 설계 및 개발하는 기술, (2) IP를 검증하고 테스트하는 기술, (3) IP를 유통하기 위한 표준 및 인프라, (4) 나노 SoC 시스템을 물리적으로 통합하는 기술, (5) 나노 SoC 시스템에 필요한 부품 기술로 나눌 수 있음

| 표준화대상항목           | 정의                        | 세부 표준화 대상항목           | 표준화 내용 소개                                 |

|-------------------|---------------------------|-----------------------|-------------------------------------------|

|                   |                           | HDL Coding            | HDL 언어 표준 확장 및 시스템을 기술(description)하는 방법  |

| IP                | IP를 설계 및 개발하는 기술          | IP Interface          | IP 상호 연결을 위한 연결 방법                        |

| 설계 기술             | IF글 걸게 낮 게걸이는 기술          | AMS IP                | 아날로그/혼성신호 IP의 재사용을 위한 방법                  |

|                   |                           | Platform-Based Design | IP 재사용이 용이하도록 구성된 Platform 및 이를 사용한 설계 방법 |

| IP 검증 및<br>테스트 기술 | P를 검증하고 테스트하는 기술          | IP Test/Verification  | IP의 검증 및 테스트 방법                           |

|                   |                           | IP 전달물                | IP 사용자에게 IP가 전달될 때 재사용이 용이하도록 전달해야 할 항목   |

| IP 유통 표준          | IP를 유통하기 위한 표준 및          | IP 품질 평가              | P 사용자가 IP 구매 전에 IP의 품질에 대한 정보를 제공하기 위한 항목 |

| ₩ πô ≖c           | 인프라                       | P 보호                  | IP 거래에 있어서 법적인 IP 보호, 기술적 IP 보호에 대한 방법    |

|                   |                           | IP Numbering          | IP 유통 및 관리가 용이하게 하기 위한 표준화된 넘버링 방법        |

| 시스템 통합<br>기술      | 시스템을 물리적으로 통합하<br>기 위한 기술 | Chip-Package Codesign | 다수의 Chip과 Package를 물리적으로 통합하기 위해 공유해야할 항목 |

| 시스템 부품            | 시스템에 필요한 각종 부품            | 센서 부품                 | 다양한 센서 부품 기술 및 시스템에 통합하기 위한 연결 방법         |

| 기술                | 기술                        | 초고주파 부품               | 다양한 초고주파 부품 기술 및 시스템에 통합하기 위한 연결 방법       |

### 1.1.2. 연관기술 분석

### ○ 연관기술 관계도

# ○ 연관기술 분석표

| dalak             | ıll Q                            | 표준화기              | l구/단체             | 표준회        | 하수준        | 기술개  | 발수준           |

|-------------------|----------------------------------|-------------------|-------------------|------------|------------|------|---------------|

| 연관기술              | 내 용                              | 국내                | 국외                | 국내         | 국외         | 국내   | 국외            |

| 반도체 소자            | 반도체 칩 설계를 위한 소자 설계/분석/측정 기술      | _                 | IEC               | -          | -          | 상용화  | 상용화           |

| 반도체 공정            | 반도체 칩 제작을 위한 제조 기술               | -                 | SEMI              | -          | -          | 상용화  | 상용화           |

| System-in-Package | 다수의 칩을 단일 패키지로 집적하는 시스템<br>통합 기술 | _                 | ITRS,<br>JEDEC    | -          | -          | 기술기획 | 시제품/<br>프로토타입 |

| CAD               | 회로 설계를 위한 설계 자동화 기술              | SoC Forum<br>/TTA | SI2/<br>Accellera | 표준<br>제/개정 | 표준<br>제/개정 | 상용화  | 상용화           |

| RF                | 초고주파를 위한 소자, 회로, 부품 기술           | _                 | _                 | -          | ı          | 상용화  | 상용화           |

| Embedded Memory   | SoC 내부에 메모리를 내장하는 기술             | -                 | -                 | -          | -          | 상용화  | 상용화           |

| Sensor            | 물리량, 화학물질 등을 감지하는 센서 기술          | _                 | IEC               | _          |            | 상용화  | 상용화           |

| Multimedia        | 멀티미디어 압축, 처리, 재생, 저작권 기술         | MPEG<br>Korea     | ISO/ITU-T         | 표준<br>제/개정 | 표준<br>제/개정 | 상용화  | 상용화           |

### 1.2. 추진경과 및 중점 추진방향

### ○ 추진경과

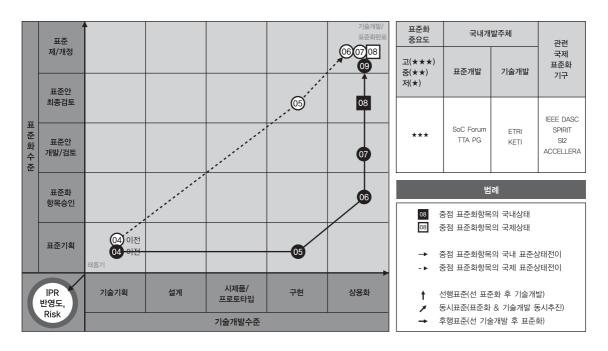

- 나노 SoC의 전 단계인 IT SoC는 Ver.2005부터 중점기술로 선정되었으며, Ver.2008부터 IT SoC의 다음 단계인 나노 SoC가 중점기술로 선정되었음

- Ver.2005에는 SoC의 설계에 핵심 요소인 IP 설계 기술, IP의 유통 표준, IP 검증 및 테스트 기술과 관련된 표준화 항목을 중점 표준화항목으로 선정함

- Ver.2006에는 표준화 대상항목인 IP 유통 표준, IP 설계 기술, IP 검증 및 테스트 기술의 3가지 요소 기술에 관련된 세부 대상항목 중 IP 전달물 표준, IP 품질평가 표준, IP 보호 표준, IP Numbering 표준, HDL Coding 방법, IP Interface, AMS IP 설계, Platform 기반 설계, IP Test/Verification 기술에 대한 중점 표준화항목에 대해서 로드맵을 보완함

- Ver.2007에는 Ver.2006의 내용을 보완하였으며, 특히 SIPAC 사업이 종료(2006년)됨에 따라 국내 표준안 의 추진 체계 및 로드맵을 수정 보완함

- Ver.2008에는 IT SoC의 다음 단계인 나노 SoC로 발전하면서 기존의 IP 기술 일변도에서 시스템 전체를 포 괄하는 방향으로 선회함. 이에 따라 시스템 통합 기술을 새롭게 중점 표준화항목으로 추가하였으며, 표준화 대상항목도 기존의 IP 설계 기술, IP 검증 및 테스트 기술, IP 유통 표준에 덧붙여서 IP 통합 기술이 추가됨

| 항목       | Ver.2005                                     | Ver.2006                                     | Ver.2007                                     | Ver.2008                                                                            | Ver.2009                                                                                                                  |

|----------|----------------------------------------------|----------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| 추진<br>경과 | - 표준화 대상으로 처음<br>선정됨<br>- 기술 표준화 대상 항목<br>확정 | - 다수의 기술 표준화<br>대상 항목 및 로드맵<br>보완            | - SIPAC 사업 종료에<br>따라 추진 체계 및 로<br>드맵 수정 보완   | - 기존의 IP 기술 일변도<br>에서 시스템 전체를 포<br>괄하는 방향으로 선회<br>- 다수의 기술 표준화<br>대상 항목 및 로드맵<br>보완 | - 표준화가 어려운 IP 검<br>증 및 테스트 기술의<br>삭제<br>- 시스템에 필요한 각종<br>부품 기술의 추가<br>- 다수의 기술 표준화<br>대상 항목 및 로드맵<br>보완<br>- 가이드라인 형태로 추진 |

| 중점<br>기술 | - IP 유통 표준<br>- IP 설계 기술<br>- IP 검증 및 테스트 기술 | - IP 유통 표준<br>- IP 설계 기술<br>- IP 검증 및 테스트 기술 | - IP 유통 표준<br>- IP 설계 기술<br>- IP 검증 및 테스트 기술 | - IP 설계 기술<br>- IP 검증 및 테스트 기술<br>- IP 유통 표준<br>- IP 통합 기술                          | - IP 설계 기술<br>- IP 유통 표준<br>- 시스템 통합 기술<br>- 시스템 부품 기술                                                                    |

#### ○ 중점 추진방향

- Ver.2009에서는 Ver.2008에서 기술 표준화에 어려움이 많은 IP 검증 및 테스트 기술이 빠지고, 시스템 전체를 포괄한다는 의미에서 시스템에 필요한 각종 부품 기술이 추가되어 IP 설계 기술, IP 유통 표준, 시스템 통합 기술, 시스템 부품 기술을 표준화 대상항목으로 결정하고, 이에 따라 HDL 코딩, IP Interface, IP 전달 물, IP 품질 평가, IP 보호, Chip-Package Codesign, Sensor 부품을 중점 표준화항목으로 결정함

- 현재까지 Ver.2008을 기반으로 SoC Forum 및 TTA PG407에서 작성한 표준화 작업이 상당한 가시적 성과 물을 보이고 있으므로 Ver.2009에서는 이를 바탕으로 시스템 전체를 포괄하는 방향으로 Ver.2008을 수정 보위하고자 함

- Ver.2009에서 처음으로 추가된 시스템 부품 기술의 경우 국내외 산업체의 부품 기술이 개별 산업체마다 상이하므로, 세부 항목까지 규정되어 강제성을 띤 기술 표준 형태보다는 개별 산업체의 제작 기술 차이를 존중하면서도 설계자의 시간과 노력을 줄일 수 있는 가이드라인 형태를 개발하고자 함

- Ver.2009에 중점 표준화항목으로 선정되지는 않았으나 향후 매우 중요한 위치를 차지할 것으로 생각되는 RF, Power IC, Biochip, Telemetric, Low-Power 등의 유망 핵심기술의 표준화가 향후 수년 이내에 필요 하게 될 것으로 생각되며, Ver.2010부터는 이들 유망 핵심기술에 대해 기술 및 시장 발전 상황을 면밀하게 살펴가면서 일정 궤도에 오른 항목부터 중점 표준화항목으로 선정하는 방안을 적극 검토할 예정임

### 1.3. 표준화의 Vision 및 기대효과

IT기술과 System-on-Chip 반도체 강국 1단계('04~'08) 2단계('09~'11) 3단계('12~'18) 비전 및 목표 국제 표준안 동조 국내 표준의 국제화 국제 표준 선도 - 표준안 수용, 적용 - 표준화와 기술 개발 연계 - 나노 SoC 기술 표준 선도국 기술적 효과 경제적, 사회적 효과 • 총 생산 유발 2.5조 원 • SoC 핵심기술 개발 촉진 → 경쟁력 강화 • 총 고용 창출 5만 명 • 유통 표준화: Time to Market 단축 → • 저비용으로 양질의 IT 서비스 제공 IT SoC 산업의 성장 및 활성화 •IT-SoC 시장의 체계적 발전 Partnership People • IPR 확보 가능한 • 연구인력에 표준관련 • Asian IP/SoC 미팅을 • IP 개발/등록 시 항목 표준화와 교육 강화 통한 협력 표준 활용 권장 • IP 표준의 중요성 기술개발과 공조 • 표준관련 강좌 개발 • 국내 유관기관 협력 • IPR 권리지도 작성 • 표준 전문가 풀 육성 홍보 강화 지원 IP 설계 기술 IP 유통 표준 시스템 통합 기술 시스템 부품 기술 R&D 및 표준화 • HDL Coding • IP 전달물 · Chip-Package • Sensor 부품 • IP Interface • IP 품질평가 Codesign

• IP 보호

#### 1.3.1. 표준화의 필요성

나노 SoC는 (1) 서로 다른 분야, 서로 다른 기관, 서로 다른 팀에서 SoC 개발에 참여하는 설계자 및 개발자들이 상호 협력하여 대규모 SoC의 설계를 가능하게 하고, (2) 설계자 및 개발자와 수요자 사이에 SoC 설계물 및 결과물에 대한 공유, 평가, 교환, 유통, 검증 등을 가능하게 하기 위해 표준화가 절실히 필요함

- 나노 SoC는 정보통신기기의 핵심기능을 처리하는 메모리, 디지털 회로, 아날로그 회로, CPU, 센서 등이 통합된 복잡한 시스템을 하나의 반도체 칩에 집적하는 기술임

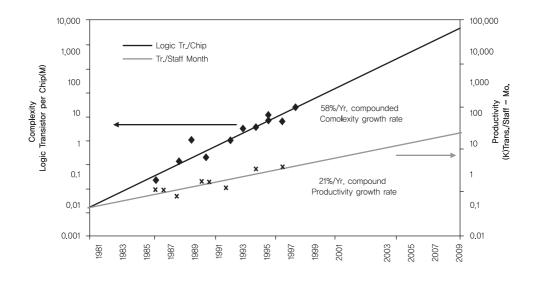

- 이러한 나노 SoC의 개발을 위해서는 통신, 컴퓨터, 정보기기 등 "시스템 기술"과 집적회로 설계 및 검증 등 "반도체 기술"이 융합되어야 함. SoC 설계 기술의 핵심은 수천만 개에서 수억 개가 넘는 트랜지스터로 구성된 복잡한 SoC를 어떻게 설계, 검증, 테스트할 것인가 하는 문제임. 설계와 개발의 복잡도는 증가하는 반면에 시장에서 요구하는 제품개발 시간은 점점 더 짧아지고 있음. 따라서 Time─to Market의 해결이 극복하여야 할 중요한 문제임

〈설계 및 개발의 복잡도 증가와 설계자의 생산성 증가〉

(Source: Sematech)

○ 이러한 SoC 설계의 복잡성, 기술의 다양성 및 시간제약 문제를 극복하기 위해서는 동작이 검증된 IP를 재사용하여 SoC를 설계하는 방법이 필요하게 되었음. IP를 재사용하여 SoC를 설계하는 방법은 초기에는 복잡한

ASIC을 위해서 필요한 기능을 만족하는 IP를 사용하여 설계하는 Block 기반 설계(Block Based Design)방법 이 사용되었으나, 현재는 미리 검증된 IP의 재사용을 위한 시스템의 구성을 설계하고 IP뿐만 아니라, 시스템의 기본 구성도 재사용하여 시스템을 개발하는 Platform 기반 SoC 설계 방법(Platform Based Design)으로 발전 하였음

- 비록 설계 기술 및 설계 도구의 발달에 따라 설계자의 생산성도 증가하고 있으나, 시스템 규모의 증가 추세가 훨씬 더 급격하기 때문에 하나의 SoC를 개발하는데 필요한 IP의 수 및 설계자의 수는 점점 증가하게 됨 이에 따라 다수의 설계자가 만든 다수의 IP를 다수의 설계자가 하나의 SoC로 구성하는 경우가 더욱 빈번해졌음

- 시스템 규모가 급격하게 커짐에 따라 시스템의 주요 성능과 구조를 설정하는 시스템 개발자, 시스템의 H/W를 구현하는 H/W 개발자, 시스템 위에 S/W를 구현하는 S/W 개발자 등이 SoC 구현 과정에서 상호 긴밀하게 협력해야 할 필요성이 급격히 증가하였음

- 상업적으로 개발된 IP의 성능이 높아짐에 따라 플랫폼 위에서 이미 검증된 IP를 재사용하는 것이 설계 시간 및 비용 단축에 유리하는 경우가 많아졌음. 이 경우 IP의 제작, 검증, 품질 평가, 유통, 부정사용에 대한 기술적인 보호 등에 대한 필요성이 급격히 증가하였음

- O SoC 구현 면에서 IP뿐만 아니라 다수의 설계자가 개발한 SoC 칩을 단일 패키지 위에 집적하는 System-in-Package(SiP) 기술이 발전하였으며, 이에 따라 다수의 칩과 패키지를 통합하여 설계하는 Chip-Package Codesign 기술의 필요성이 급격히 증가하였음

- 또한 SoC 구현 면에서 아날로그 회로와 디지털 회로 이외에 센서, RF, 메모리, MEMS 등의 각종 부품이 단일 SoC에 집적되기 시작되었으며, 이에 따라 시스템에 필요한 각종 부품 기술의 중요성이 급격히 증가하였음

- 따라서 나노 SoC 분야에서 IP 설계 기술의 표준화, IP 유통 표준 제정, 시스템 통합 기술의 표준화, 시스템 부품 기술의 표준화 등이 절실하게 요구되고 있음

- 특히 정부의 정책이 SoC 관련 시스템 부품에 집중되기 시작한 점을 감안하여 정부의 정책에 부합하는 방향으로 표준화가 진행되어야 함

#### 1.3.2. 표준화의 목표

나노 SoC 기술의 근간이 되는 IP 개발 산업이 활성화 될 수 있도록, IP 설계 기술, IP 유통 표준, 시스템 통합 기술, 시스템 부품 기술에 대한 표준화를 추진

- IP의 설계, 검증, 테스트, 유통 등을 위한 표준안 제정

- 시스템 통합 및 시스템 부품 등을 위한 표준안 제정

- 국제 표준화 추진 기구의 표준 제정에 대응하는 국내 표준안 마련

- 중국, 일본, 대만 등과의 협력을 통하여 아시아의 표준을 주도

#### 1.3.3. Vision 및 기대효과

나노 SoC 핵심 기술 개발 촉진을 통한 System-on-Chip 반도체 강국 실현

- 국내 총생산 2.5조 원 유발, 국내고용 5만 명 창출

- 저비용으로 양질의 IT 서비스를 제공하고 IT 정보화 사회를 촉진

- O SoC 핵심기술 개발 촉진을 통한 한국 반도체 산업의 경쟁력 향상

- SoC 설계기술의 유통 표준 제시를 통한 SoC시장의 체계적인 발전 및 활성화 촉진

# 2. 국내외 현황분석

### 2.1. 시장 현황 및 전망

#### 2.1.1. 국내 시장 현황 및 전망

○ 국제 시장 조사 기관인 IDC에 따르면 국내 SoC 시장 현황 및 전망은 아래 표와 같으며 연평균 성장률은 생산 규모의 경우 연 14,0%, 수출 규모의 경우 연 12,8%의 고속 성장이 예상되고 있음

〈국내외 SoC 시장 현황 및 전망〉

| ā   | 구 분  | 2002  | 2003  | 2004  | 2005  | 2006  | 2007  | 2010  | CAGR(%) |

|-----|------|-------|-------|-------|-------|-------|-------|-------|---------|

|     |      | 1,407 | 1,645 | 1,872 | 2,091 | 2,412 | 2,601 | 3,763 | 13.1    |

| 세계  | 메모리  | 284   | 343   | 388   | 417   | 454   | 520   | 748   | 12.9    |

| 시장  | SoC  | 925   | 1,074 | 1,227 | 1,385 | 1,638 | 1,732 | 2,525 | 13.2    |

|     | 개별소자 | 198   | 228   | 257   | 289   | 320   | 349   | 490   | 12,0    |

| 7.1 | 생산   | 263   | 307   | 352   | 393   | 453   | 492   | 753   | 14.0    |

| 국내  | 수출   | 166   | 196   | 215   | 239   | 266   | 310   | 435   | 12,8    |

(IDC, 2002.4)

○ 국내 중소 벤처업체의 주요 IP 활용실적을 IT—SoC 협회의 통계자료를 통하여 살펴보면, 2003년도 중소벤처 업체가 삼성전자와 하이닉스반도체에서 제작한 SoC는 총 78건이며, 이에 사용된 IP는 총 124건임(아래 표 참조). 가장 많이 사용된 IP는 ADC, DAC 및 PLL 등의 아날로그 Hard IP로 전체의 60%를 차지함. 내장형 프로세서 코어는 ARM을 대부분 사용하였고, 고속 인터페이스 IP로는 USB가 대부분을 차지함. 사용된 아날로그 IP는 공정 의존적이고 매크로 셀 성격으로 대부분 국내에서 개발된 국산 IP 이지만, 프로세서 코어와 BUS 인터페이스 등의 디지털 IP는 거의 도입된 외산 IP를 사용하였음

〈삼성과 매그나칩의 Foundry 서비스를 통한 '03년도 IP 사용 현황(IT-SoC 산업동향, '04.12)〉

| 구분          | 삼성전자 | 매그나칩 | 합 계 | 구성비(%) |

|-------------|------|------|-----|--------|

| 프로세서 코어     | 20   | 6    | 26  | 21,0   |

| ARM 코어      | 19   | 4    | 23  | 18.5   |

| 80C51 외     | 1    | 2    | 3   | 2,4    |

| 아날로그 IP     | 58   | 17   | 75  | 60.5   |

| ADC/DAC     | 32   | 7    | 39  | 31,5   |

| PLL         | 26   | 10   | 36  | 29.0   |

| 고속 인터페이스 IP | 15   | 8    | 23  | 18,5   |

| USB         | 13   | 6    | 19  | 15,3   |

| PCI 외       | 2    | 2    | 4   | 3,2    |

| 합 계         | 93   | 31   | 124 | 100    |

| (적용 SoC)    | 60   | 18   | 78  | _      |

○ 국내 반도체 제조업체의 IP 보유 현황을 살펴보면, 국내의 삼성전자, 매그나칩, 동부아남반도체 등 반도체 제조업체 3사가 보유하고 있는 0.13/0.18/0.25um 지원 IP는 총 287건임. 이중 삼성전자가 전체 보유 IP 건 수의약 74%를 차지하고 있으며, 매그나칩이 15%, 동부아남반도체가 12%를 차지하고 있음(다음 표 참조). 아날로그 IP는 공정 의존적이고 매크로셀 성격으로 대부분 국내에서 자체개발한 IP이며, 그 외의 디지털 IP는 거의 도입된 외산 IP임. TSMC가 IP Alliance Program에서 제공하는 IP 건수는 0.13um 31종, 0.18um 51종, 0.25um 34종인데 비하여, 삼성전자의 경우 ARM 코어만 47종의 IP를 제공하는 등 0.25um 이후의 첨단 SoC 개발에 필수적인 풍부한 IP를 제공하고 있어 세계적인 팹리스 업체로부터 환영을 받고 있지만, 대량생산 위주의 SoC 제품 위주로 지원되기 때문에 국내 중소업체가 이용할 수 있는 기회는 극히 제한적인 문제점이 있음. 삼성전자를 제외한 국내 반도체 제조업체를 이용하여 SoC를 제작할 경우 지원되는 IP의 부족으로 인하여 중소업체가 직접 필요한 IP를 라이센스 하여야 하며 이 경우 발생되는 IP 사용료의 비용부담이 국내 SoC 산업 발전의 장애요소임

〈국내 반도체 제조업체의 보유 IP 현황〉

| 구분            | 0.13um |     | 0.18um |    |    | 0.25um |    | 합계  |

|---------------|--------|-----|--------|----|----|--------|----|-----|

| ↑ 世           | 삼성     | 삼성  | 매그나칩   | 동부 | 삼성 | 매그나칩   | 동부 | 업계  |

| 프로세서 코어       | 38     | 25  | 6      | 8  | 10 | 7      | 5  | 99  |

| ARM 코어        | 26     | 17  | 1      | 1  | 4  | 2      | 0  | 51  |

| 80C51 외       | 0      | 0   | 5      | 6  | 0  | 5      | 4  | 20  |

| DSP 코어        | 12     | 8   | 0      | 1  | 6  | 0      | 1  | 28  |

| 아날로그 IP       | 18     | 25  | 14     | 4  | 19 | 13     | 11 | 104 |

| ADC/DAC       | 9      | 17  | 11     | 2  | 16 | 10     | 5  | 70  |

| PLL           | 9      | 8   | 3      | 2  | 3  | 3      | 6  | 34  |

| 고속 인터페이스 P    | 15     | 17  | 1      | 1  | 8  | 2      | 2  | 46  |

| USB           | 6      | 5   | 0      | 1  | 2  | 1      | 2  | 17  |

| PCI 외         | 9      | 12  | 1      | 0  | 6  | 1      | 0  | 29  |

| Peripheral IP | 36     | 36  | 0      | 0  | 36 | 0      | 0  | 36  |

| Multimedia 등  | 0      | 0   | 0      | 1  | 0  | 0      | 1  | 2   |

| 합 계           | 107    | 103 | 21     | 14 | 73 | 22     | 19 | 287 |

(IT-SoC 산업동향, 2004.12)

- 국내 센서 및 MEMS 관련 소자의 시장규모는 2002년 16억 불에서 2007년 21억 불로 성장하였으며, 2012년에는 약 34억 불정도로 연평균 7.8%의 높은 성장률을 보이고 있는 것으로 조사됨. 우리나라 센서시장의 규모는전 세계 시장의 대략 17.1%를 점유하고 있으며, 이는 규모의 측면에서 살펴볼 때 6위의 위치를 차지하고 있음. 센서소자의 품목별 시장규모를 살펴보면, 우리나라의 센서소자들은 주로 압력, 화학, 유량, 영상, 근접, 레벨, 온도 센서가 시장의 대부분을 차지하고 있으며, 2007년을 기준으로 할 때 압력, 화학, 유량, 영상 센서가 전체시장의 50%이상으로 센서시장의 대부분을 점유하고 있는 것으로 나타남. 이들 센서 중에서 특히 영상센서 분야는 현재 시장규모로 4위로 나타나고 있지만 연평균 시장 성장률이 11,2%로 다른 센서의 성장률의 2배 이상을 상회하는 현상을 보이고 있음. 이는 휴대폰 등 모바일용 개인 전자기기의 급속한 보급에 따라서 영상센서의 수요가 급증할 것이라는 기대를 반영하고 있는 것으로 판단됨

- 센서시장 규모는 그 응용 분야의 성장에 민감하게 반응하므로 독립적인 센서시장의 규모보다 응용분야에 따른 시장규모가 더 큰 의의가 있음. 2007년 기준으로 우리나라의 응용분야별 센서시장은 제조/공정과정에 사용되고 있는 센서가 가장 비율로 수위를 차지하고 있으며, 그 뒤를 자동차용 센서와 함께 센서시장의 거의 절반가량을 점유하고 있음

#### 〈응용분야별 국내 센서 시장 규모〉

(단위: 백만 불. %)

| 응용분야    | 2002  | 2003  | 2004  | 2005  | 2006  | 2007  | 2010  | 2012  | 성장율  |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| 자동차     | 356   | 376   | 400   | 428   | 459   | 493   | 624   | 710   | 7.1  |

| 제조/공정   | 385   | 405   | 429   | 455   | 486   | 520   | 648   | 730   | 6.6  |

| 기계/공구   | 286   | 302   | 320   | 341   | 366   | 393   | 499   | 580   | 7.3  |

| HVAC/빌딩 | 239   | 254   | 271   | 291   | 314   | 341   | 438   | 500   | 7.7  |

| OA/통신   | 53    | 57    | 60    | 65    | 70    | 76    | 99    | 120   | 8.5  |

| 기타응용    | 276   | 302   | 332   | 366   | 405   | 449   | 610   | 728   | 10.2 |

| 합계      | 1,595 | 1,696 | 1,812 | 1,946 | 2,100 | 2,272 | 2,918 | 3,368 | 7.8  |

(한국센서연구조합, 2007.6)

○ 국내 RF 부품시장은 2005년 기준으로 약 4,500억 원 정도로 추산됨. RF 부품을 생산하는 국내 주요 업체로는 삼성전기와 LG이노텍 등이 PAM을 생산하고 있으며 Duplexer는 삼성전기, Patron 등이 있고, SAW 필터는 삼성전기, LG이노텍, KEC, SAWNET, IFT, SAWVICS 등이 있고, FEM은 LG이노텍, 삼성전기 등이 있고, RFIC는 삼성전자, LG이노텍, FCI 등이 있음. PAM의 경우는 모듈을 구성하는 핵심 소자는 수입에 의존함에 따라 큰 마진을 얻지 못하는 실정이며 RFIC는 설계기술은 보유하고 있으나 IC제작을 위한 실제 공정은 해외에서 제작하는 실정임. 그러나 국내 RF 부품시장 규모가 계속 성장하여 2017년에는 4조 원 정도로 추산되므로 공정기술 확보 등이 중요할 것으로 사료됨

〈국내 RF 부품 시장 규모〉

|      | 구 분 2005년 |          | 2012년       | 2017년       |

|------|-----------|----------|-------------|-------------|

| DEH  | 시장        | 4,500억 원 | 1조 6,000억 원 | 4조 원        |

| RF부품 | 국내업체점유    | _        | 1,600억 원    | 1조 6,000억 원 |

(산업기술동향분석, 2005)

#### 〈RF 부품별 국내 개발 동향 및 주요 업체 현황〉

| 구분       | 개발동향                                                                                                                                                                                            | 주요업체                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| FEM      | — GSM 중심으로 Dual/Triple Band용 상용화<br>— GSM에서 2004년 30%의 채용율 추정<br>— CDMA는 개발 중                                                                                                                   | 해외: 무라타, 마쓰시다, EPCOS, 히타치<br>국내: LG이노텍, 삼성전기                                        |

| Duplexer | - Dielectric Duplexer 영역을 SAW Duplexer, FBAR Duplexer 등이 점<br>차 대체<br>- GSM에서는 LTCC 적층 RF FEM화를 통한 집적화 추세                                                                                       | 해외: EPCOS, 무라타, 교세라, 마쓰시다,<br>TDK, 후지쓰, 오끼전기<br>국내: 삼성전기, Patron                    |

| SAW 필터   | - 소형화, 고주파화, FEM과의 일체화<br>- SAW Duplexer 및 Dual-band SAW 필터의 수요 급증 예상<br>- GSM의 경우 Direct Conversion 채용 시 IF SAW 필터 수요 격감 예상                                                                    | 해외: 후지쓰, EPCOS, 무라타, 지멘스, 마<br>쓰시다<br>국내: 삼성전기, LG이노텍, KEC,<br>SAWNET, ITF, SAWVICS |

| PAM      | - GaAs 또는 Si 소자를 이용한 MMIC화<br>- LTCC 적층기술을 이용한 초소형 복합모듈화<br>- 초소형화 실현을 위한 베어칩 형태의 제품 출시<br>- 고효율, 저전력 소모 Si소자의 개발을 통한 IC 내 구현 기술 개발 중                                                           | 해외: RFMD, Skyworks, 커넥선트,<br>Agilent, 미쓰비시, 히타치<br>국내: 삼성전기, LG이노텍                  |

| RFIC     | <ul> <li>CMOS 공정기술을 이용한 고주파화 설계</li> <li>Multi-mode/Multi-band 고기능 RFIC 개발</li> <li>RF+BB 통합 IC개발(RFSoC)</li> <li>안테나, RF스위치, PAM, TCXO용 온도보상 IC, VCO, 필터 등의 고유 RF부품의 Si RFIC 내장화 개발</li> </ul> | 해외: TI, Qualcomm, RFMD<br>국내: 삼성전자, LG전자, FCI                                       |

(한국정보통신정책, 2005)

#### 2.1.2. 국외 시장 현황 및 전망

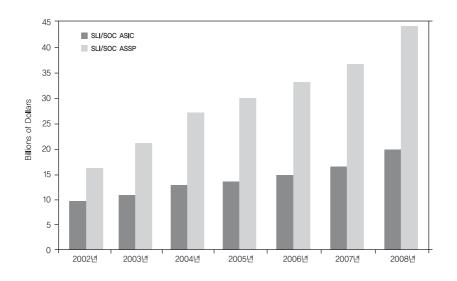

○ Gartner Dataquest에 따르면 ASIC/ASSP 중 IT SoC 규모는 2003년 315억 달러로 전체 반도체 시장 1,775억 달러에서 차지하는 비중은 17.7%이며, 연평균 15.9%의 성장률을 기록하면서 2008년에는 640억 달러에 이를 것으로 전망하였음. 이와 같은 시장 규모는 2003년 전체 ASIC/ASSP 시장의 52.9%, 2008년에는 66.9%에 해당하는 것으로서 전체 반도체 시장에서 SoC가 차지하는 비중은 시간이 지날수록 점차 증가할 것으로 예상됨

〈ASIC/ASSP 중 IT SoC 규모 추이〉

(Gartner Dataquest, 2004.11)

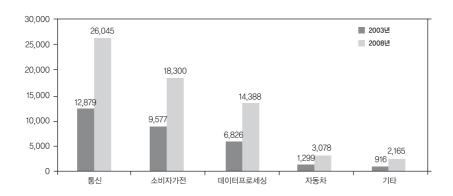

○ 현재 ASIC보다 좀 더 표준화되어 복수의 사용자가 구매하는 ASSP SoC가 전체 SoC 시장에서 차지하는 비중이 약 60~70%로 ASIC SoC보다 높음. 주요 산업별 시장 현황을 살펴보면 유/무선 통신 분야가 2003년 현재 전체 SoC 시장의 약 41%를 차지하고 있으며, 2003년 약 129억 달러에서 연평균 15.1%의 성장률을 기록하면서 2008년에는 약 260억 달러에 이를 것으로 전망됨. 소비자가전 부문은 전체 SoC 시장의 약 30.4.%를 차지하고 있으나 다른 산업에 비해 연평균 성장률이 13.8%로 저조하여 2008년에는 시장 점유율이 다소 감소할 것으로 보임. 반면 데이터 프로세싱 및 자동차 산업은 연평균 성장률이 각각 16.1%, 18.8%로 높아서 2003년 시장 점유율 21.7%, 4.1%에서 2008년에는 현재보다 소폭 증가할 것으로 보임

〈주요 산업별 SoC 시장 규모(Gartner Dataquest, 2004.11)〉

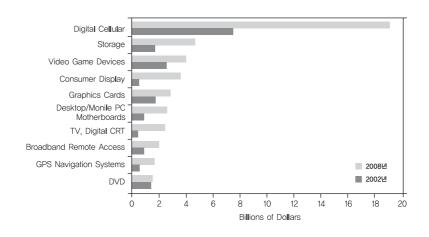

○ 주요 제품별 시장 현황은 디지털 셀룰러폰시장이 2002년 75억 불, 2003년 95억 불로 전체 SoC시장의 약 30%를 차지하여 가장 큰 비중을 차지하고 있으며 2008년에는 191억 불에 이를 것으로 전망됨. 셀룰러폰 이외에 2002년에는 비디오 게임기, 스토리지, 그래픽카드, DVD 등에 SoC가 많이 사용되고 있는 것으로 나타났으나 2008년에는 디스플레이, 디지털 TV, 모바일 PC, 스토리지 등에 사용되는 SoC시장이 크게 성장할 것으로 예상됨

〈주요 제품별 SoC 시장 규모(Gartner Dataquest, 2004.11)〉

○ MEMS 소자 및 센서의 규모는 2012년까지 140억 불에 이를 것으로 전망하고 있음. 이는 2007년 시장규모인 71억 불의 약 2배에 해당하는 규모로서 연평균 14%에 해당하는 높은 성장률로 시장이 확대되고 있음. 센서 시장규모는 자동차용 센서시장의 확대, 의료 및 바이오센서의 신시장 창출, 그리고 환경에 대한 관심의 증가로 계

속 확장되고 있음. 특히 자동차용 센서 시장규모는 전체 센서시장의 27%(2007년 기준)를 차지하고 있으며, 지속적인 성장이 기대됨. 또한 의료/바이오, 환경에 관련된 센서시장은 2002년 57억 불 규모에서 2012년 111억 불로 2배가량의 성장이 예측됨. 한편 단위 칩의 개수로 환산한 시장규모는 2007년 현재 약 25억 개의 소자가 생산되고 있으며. 2012년에는 약 67억 개의 MEMS 소자 및 센서가 생산될 것으로 예측되고 있음

〈세계 MEMS 센서 시장 예측(Yole Developmemt, 2007)〉

○ RF 부품시장 규모는 크게 반도체와 비반도체 산업으로 구분하여 파악할 수 있음. JP모건의 이동통신단말의 원 가구조 자료를 살펴보면, 전체 이동통신단말에서 RF부품이 차지하는 비중이 16.7% 정도인 것으로 나타남. 이중에서 수동부품, RF필터, VCO, TCXO 등과 같은 비반도체 부품의 비중이 11.8%로 전력증폭기, Transceiver 및 스위치와 같은 반도체 부품의 비중이 5%로 아직까지 비반도체 부품의 비중이 2배로 높게 나타나지만 향후에는 RF부품이 모듈화 및 고집적화 됨에 따라 반도체 부품의 비중이 확대될 것으로 예상됨. 2003년 iSuppli 자료에 따르면, 국외 RF 부품시장의 규모는 2005년 기준으로 약 36억 불 정도의 규모로 예상하며 성장률을 20%로 가정할 때 2017년에는 280억 불로 추정됨. 한편 2004년 Gartner 자료에 따르면, 2003년에 전력증폭기 IC는 115억 불, PAM은 1,235억 불, PLL은 168억 불, Transceiver는 3,513억 불, 기타 RF 부품이 106억 불 규모의 시장이 형성되고 있음

〈국외 RF 부품시장 규모(iSuppli, 2003)〉

| 구 분       | 2005년  | 2012년  | 2017년  |

|-----------|--------|--------|--------|

| -<br>RF부품 | 36억 불* | 120억 불 | 280억 불 |

## 〈세계 RF 부품시장 규모(Gartner Dataquest, 2004.6)〉

단위: 백만 불, %

| 구분                     | 시장규모   |        | нI    | 증가율   |                                       |

|------------------------|--------|--------|-------|-------|---------------------------------------|

| т <del>с</del>         | 2002년  | 2003년  | 2002년 | 2003년 | · · · · · · · · · · · · · · · · · · · |

| Power Amplifier IC     | 229    | 115    | 2,0%  | 0.8%  | -49.8%                                |

| Power Amplifier Module | 893    | 1,235  | 7.7%  | 8.8%  | 38,3%                                 |

| RF PLL                 | 190    | 168    | 1,6%  | 1,2%  | -11,3%                                |

| RF Transceiver         | 2,889  | 3,513  | 25,1% | 25,2% | 21.6%                                 |

| 기타 RF 반도체              | 62     | 106    | 0.5%  | 0.8%  | 71.0%                                 |

| Baseband IC            | 7,268  | 8,819  | 63%   | 63,2% | 21,3%                                 |

| <br>합계                 | 11,531 | 13,956 | 100%  | 100%  | 21.0%                                 |

### 2.2. 기술개발 현황 및 전망

#### 2.2.1. 국내 기술개발 현황 및 전망

#### ○ 정부정책기조

- 舊 정보통신부는 개인소득 2만 불 달성을 위한 국가차원의 산업육성 정책으로 2003년부터 IT839 전략을 추진하였고, 2005년에 u-IT839 전략으로 개편된 바 있음. SoC는 오랫동안 IT839 전략 및 u-IT839 전략의 핵심 산업으로 자리잡아왔음. 현 정부 출범 이후에 舊정보통신부가 舊산업자원부와 통합하여 지식경제부가 발족한 이후에도 나노 SoC는 국가 핵심 산업으로서의 위치를 확고히 하고 있으며, 지식경제부의 최고 역점 분야의 하나로 정부의 집중적인 지원을 받고 있음

- 정부의 SoC 산업 정책 기조는 신성장 동력과 직결되는 핵심부품 기술개발에 역점을 두고 차세대 성장동력 등 범부처 사업과의 연계강화를 통해 시너지를 극대화하는 것임. 이를 위하여, IT 산업의 고부가가치화를 위한 핵심부품개발을 강화, 시스템의 경쟁력 확보를 위해 필수적인 품목을 집중지원 육성, 차세대 전략 분야의 리더십 확보를 위한 국제 표준화 지원을 강화, 차세대 이동통신 등 국내 선도 기술을 국제 표준에 전략적으로 반영하고 한·중·일 표준화 협력 등을 통한 제휴를 확대하고 기술개발-표준화-인력양성 사업간 연계를 강화하고 있음. 기술개발 수행기관 등 R&D 사업의 수행 주체 간에 협력 네트워크를 강화하며 차세대 성장 동력 산업의 성과 제고를 위한 End product 중심의 기술개발과 IT 강국의 질적 도약을 위한 핵심원천기술 개발을 병행하고 있음

#### ○ 국책연구소

- 국책연구소는 주로 한국전자통신연구원(ETRI) 및 전자부품연구원(KETI)을 주축으로 SoC 연구가 진행되고 있으며, 특히 ETRI는 SoC 산업 진흥센터를 통해 SoC에 관련된 산학연 연구 역량을 집결하는 시스템을 구축 하였음

- ETRI는 SoC산업진흥센터를 운영함으로써 (1) SoC 산업에 필요한 고급 설계 인력의 양성, (2) SoC 산업에 필요한 기반 기술 및 설계 기술의 개발, (3) 중소 벤처업체를 위한 HW, SW, 에뮬레이션, 시험장비, 설계환경의 지원, (4) 창업보육사업과 마케팅 네트워크 구축 및 국내외 협력추진 사업을 수행 중에 있음

- 또한 ETRI는 융합부품 · 소재부문을 설립하여 미래 유망 산업인 융합 기술의 구현 기술로서 SoC 기술을 적 극 연구 개발하고 있으며, 각종 대형 국책 연구과제를 통해 IT 산업의 핵심인 중장기 대규모 연구개발 사업으로 미래 성장 동력을 위한 원천기술을 개발하고 있음. 또한 IT 신성장동력 및 핵심 인프라 기술개발, 부가 가치 제고를 위한 핵심부품개발을 진행하고 있음

#### ○ 산업계

- 국내 산업계는 크게 SoC 설계 개발 회사, SoC 생산 회사, 파운드리 서비스 업체로 구분할 수 있으며 국내 SoC 기업의 주요 제품은 메모리 부품과 디스플레이 관련 부품, 멀티미디어 관련 부품 등을 들 수 있음

- 메모리 부품은 DRAM, SRAM, 플래시 메모리가 주력을 이루고 있으며, 명실공히 세계 최고의 기술력과 시장 점유율을 가지고 있음. 특히 삼성전자와 하이닉스 반도체는 각각 세계 1위와 3위의 메모리 생산 업체로서국내 SoC 산업을 선도하고 있음

- 디스플레이 부품은 크게 디스플레이 패널 자체의 생산과 디스플레이 구동용 반도체인 LDI(LCD Driver IC) 를 들 수 있으며 세계 최고 수준의 기술력과 시장 점유율을 가지고 있음

- 멀티미디어 부품은 초기에는 휴대전화에 사용되는 CIS(CMOS Image Sensor) 제품으로 시작하여 CCP(Camera Control Processor), CSP(Camera Signal Processor), MMP(Mobile Multimedia Platform) 로 확대되고 있음

- 국내 반도체 산업은 제조 분야에서는 메모리 제품 중심, 설계 분야에서는 디스플레이 부품 및 멀티미디어 부품 중심으로 발전하였으며, 주문에 의한 반도체 생산을 담당하는 파운드리 분야는 크게 활성화되지 못하고 있음

- 최근 한국반도체산업협회와 통합된 IT-SoC 협회에는 100여 개의 국내 중소 IT-SoC 전문 업체가 가입되어 있으며, 엠텍비젼, 코아로직 등 휴대전화의 멀티미디어 칩 관련 제품을 공급하는 회사가 국내선도 기업으로 자리 잡고 있음

#### ○ 학계

- 국내 대학은 일찍부터 SoC 설계 인력 양성 및 설계 기술 개발에 노력해왔으며, 한국과학기술원의 IDEC(IC Design Education Center), 서울대학교의 SoC 설계 기술 사업단, 광운대학교의 IP/SoC 사업단 등의 대형 사업단, 기타 지식경제부와 교육과학기술부의 지원을 받는 다수의 ITRC와 ERC를 통해 활발한 인력 양성 및 기술 개발이 이루어지고 있음

#### 2.2.2. 국외 기술개발 현황 및 전망

#### 이 미국

- 미국은 SoC 분야에서 세계선도 기업인 Intel과 Qualcomm 등 다수의 기업을 보유하고 있기 때문에 정부 차원에서 SoC 산업을 지원하고 있지는 않지만 이들 기업이 세계 반도체 시장을 자체적으로 선도하고 있음. 특히 SoC 설계 도구(CAD). SoC 설계 기술 개발에 있어서는 거의 독보적인 위치를 차지하고 있음

- 표준화 측면에서는 VSIA(Virtual Socket Interface Alliance)를 통하여 IP 설계 기술, IP 유통 표준, IP 검증 및 테스트 기술 등의 분야에서 많은 표준화 작업을 주도적으로 진행하였으며, 2007년 이후 IEEE DASC(Design Automation Standards Committee)에서 이들 표준화 작업을 계승하여 진행하고 있음

| (2007년 1분기 세계 반도체 | 매출액 기준 20대 기업(IN Ir | nsights, 2007.5) |

|-------------------|---------------------|------------------|

|                   |                     |                  |

| 순위 | 기업      | 국가 | 순위 | 기업        | 국가 |

|----|---------|----|----|-----------|----|

| 1  | ntel    | 미국 | 11 | Micron    | 미국 |

| 2  | Samsung | 한국 | 12 | Freescale | 미국 |

| 3  | Toshiba | 일본 | 13 | Qimonda   | 유럽 |

| 4  | TI      | 미국 | 14 | NEC       | 일본 |

| 5  | Hynix   | 한국 | 15 | Qualcomm  | 미국 |

| 6  | ST      | 유럽 | 16 | Infineon  | 유럽 |

| 7  | Renesas | 일본 | 17 | AMD       | 미국 |

| 8  | TSMC    | 대만 | 18 | Elpida    | 일본 |

| 9  | Sony    | 일본 | 19 | IBM       | 미국 |

| 10 | NXP     | 유럽 | 20 | Fujitsu   | 일본 |

### ○ 유럽

- 유럽은 예전에 비해 SoC 산업에서의 경쟁력이 많이 약화되었으나, 그럼에도 불구하고 강력한 핵심 기술을 가진 다수의 기업이 포진하고 있음. 대표적인 기업으로는 세계 최대의 IP Core 공급자인 ARM을 들 수 있음

- 유럽은 국가 간의 공동 연구가 활발하게 이루어지고 있으며, 벨기에의 IMEC이 기초 연구를, 프랑스의 D&R 이 IP 유통 센터를, 스웨덴의 SoCware가 연구 클러스터를 형성하고 있음

- 표준화 측면에서는 최근 들어 SPIRIT(Structure for Packaging, Integrating, and Reusing IP within Tool Flows)를 통하여 미국의 VSIA에 맞서 IP 설계 기술, IP 유통 표준, IP 검증 및 테스트 기술 등의 분야에서 많은 표준화 작업을 진행하고 있음. SPIRIT가 개발한 표준은 IEEE 표준안의 예비 단계인 P1685로 승인 받아 IEEE 표준안으로 자리 잡을 전망임

#### ○ 일본

- 한때 세계 최고의 반도체 강국이었던 일본은 최근 들어 SoC 산업에서의 경쟁력이 많이 약화되었는데, 그 이유로는 일본의 반도체 기업들이 대부분 종합 전자회사의 일부로서 설계에서 판매까지 포괄적으로 담당하고 있기 때문에 특정 제품에 집중하기 보다는 다양한 제품을 폭넓게 취급하였기 때문에 특정 분야에 집중해야할 기술 개발과 제품 생산이 분산되었기 때문으로 생각됨

- 이러한 문제점을 타개하기 위해 일본에서는 반도체 분야의 합병이 활발히 이루어졌는데 르네사스(Renesas), 엘피다(Elpida)가 대표적인 예임. 또한 국가적으로 산학협력을 지원하기 위해 STARC(Semiconductor—Technology Academic Research Center)를 설립하여 기술 개발 및 인력 양성에 노력하고 있음

### ○ 대만

- 대만은 전통적으로 PC를 비롯한 전자 부품 및 전자 제품 산업이 발달하였으며, 이를 바탕으로 수많은 팹리스 업체가 발달하였고, 세계 1, 2위의 파운드리 업체인 TSMC와 UMC가 세계 파운드리 시장의 70% 이상을 점유하고 있음 대만의 반도체 기업은 파운드리, 어셈블리, 테스트 가운데 공정이나 특정 분야에 특화된 기업이 많고 이들 기업군이 체계적인 분업 구조를 형성하고 있음

- 연구 개발 측면에서는 1974년 설립된 ITRI(Industrial Technology Research Istitute) 산하의 ERSO(Electronic—Research & Service Organization)와 STC(SoC Technology Center)가 국가 규모의 SoC 기술 개발 및 인력 양성을 주도하고 있음

### 2.3. 표준화 현황 및 전망

### 2.3.1. 국내 표준화 현황 및 전망

#### O TTA

정부는 TTA를 중심으로 SoC 표준화를 지원하고 있으며, TTA에서는 SoC 프로젝트 그룹인 PG407을 구성하여 SoC 표준화 활동을 진행하고 있음. 현재 PG407에서는 IP 등록 표준(2005), IP Numbering 표준 (2006), SoC 설계 사양 표준(2007)이 제정되었고, IP계약서 표준(2008), IP 품질 보증 표준(2008), SoC 등록 표준(2008)이 제정 중에 있으며, IP 전달물 표준, HDL Guideline등을 추진 중에 있음

#### O SoC Forum

- TTA가 지원하고 한국반도체산업협회가 주관하는 SoC Forum은 산·학·연 전문가 들이 모여 국내 SoC 분야의 기술/정책 방향 수립 및 표준화 추진 등의 역할을 수행하고 있음. SoC Forum은 자문위원회, 운영위원회, 분과위원회로 구성되었으며, SoC 산업 관련 기업, 대학, 기관 등이 모여 의견을 교류, 상호 협력을 활성화하는 역할을 수행함

#### O Asian IP/SoC Meeting

- Asian IP/SoC Meeting은 한국의 IT-SoC 협회, 일본의 IPTC, STARC, 대만의 SoC Consortium, VDEC 등의 기관이 모여, 2002년 가을부터 아시아권 국가들의 IP/SoC 산업 발전에 대하여 논의하는 컨소시엄임. 2002년부터 매년 봄, 가을 두 번의 회의로 진행되며, 장소는 한국, 일본, 대만 3국이 돌아가며 개최하고 있음

- 아시안 IP/SoC 기술회의는 VSIA가 주도하고 있는 표준화 추진과는 차별화된, 유통 및 데이터베이스 공유를 위한 IP 분류법, IP 평가 항목 등을 주제로 논의되고 있으므로 추후 국제 유통 표준을 선도할 수 있는 기회가 될 것이라 예상됨

- 현재 Asian IP/SoC Meeting이 공동 협의하고 있는 사항은 (1) HDL 코딩 방법을 포함한 IP 품질 평가 표준 공동 제정. (2) IP 데이터베이스 공유. (3) IP 유통을 위한 IP Numbering 표준 공동 제정 등임

#### 2.3.2. 국외 표준화 현황 및 전망

○ SoC 관련 표준화는 미국의 VSIA를 중심으로 진행되어 왔으나, 2007년 7월로 그 활동을 종료하고 표준 제정 등의 작업을 IEEE DASC를 비롯한 타 기관으로 이관하였음. VSIA를 계승한 IEEE DASC의 표준화 작업은 공신력 있는 국제학회인 IEEE가 SoC 관련 표준화를 직접 진행한다는 면에서 보다 발전적인 의미를 가짐

O VSIA는 그 활동을 종료하였으나 지금까지의 결과물이 폐기된 것은 아니며, 오히려 IEEE DASC로 이관되면서 좀 더 널리 보급될 것으로 보임. 활동 종료 전까지 VSIA가 발표한 Specifications, Standards, Technical Documents는 다음과 같음

### 〈VSIA의 Specifications(2007년 7월 현재)〉

| Document Name                                                                           | Version | Authors                                 | Date Issued                        |

|-----------------------------------------------------------------------------------------|---------|-----------------------------------------|------------------------------------|

| Analog/Mixed-Signal VSI Extension<br>Specification(AMS 1.2.2)                           | 1,2,2   | Analog/Mixed-Signal DWG                 | Revised 2001,2<br>Released 1999,11 |

| Analog/Mixed-Signal Signal Integrity VSI Extension Specification(AMS 2,1,0)             | 1.0     | Analog/Mixed-Signal DWG                 | Revised 2002,3<br>Released 2002,3  |

| On-Chip Bus Attributes Specification(OCB 1.2.0)                                         | 1       | On-Chip Bus DWG                         | Revised 2001,9<br>Released 1998,8  |

| Signal Integrity Specification(IMP 1.2.0)                                               | 1       | SI Sub-DWG of the<br>Implementation DWG | Released 2004,1                    |

| Soft and Hard VC Structural, Performance and Physical Modeling Specification(I/V 1,2,1) | 2,1     | Implementation/Verification<br>DWG      | Revised 2001,1<br>Released 1999,5  |

| VC/SoC Functional Verification Specification(VER 2.1.0)                                 | 1       | Functional Verification DWG             | Released 2004,3                    |

| Test Data Interchange Formats and Guidelines for VC Providers Specification(TST 1.1.1)  | 1       | Manufacturing Related Test<br>DWG       | Revised 2001,1<br>Released 1999,6  |

| Virtual Component Transfer Specification(VCT 1,2,1)                                     | 2       | Virtual Component Transfer<br>DWG       | Revised 2001,1<br>Released 1999,10 |

### 〈VSIA의 Standards(2007년 7월 현재)〉

| Document Name                                                                                            | Version | Authors                                 | Date Issued                                  |

|----------------------------------------------------------------------------------------------------------|---------|-----------------------------------------|----------------------------------------------|

| System-Level Interface Behavioral Documentation Standard(SLD 1,1,0)                                      | 1       | System-Level Design DWG                 | Revised 2000,3<br>Released 2000,3            |

| Test Access Architecture Standard(TST 2,1,0)                                                             | 1       | Manufacturing-Related Test<br>DWG       | Revised 2001,9<br>Released 2001,9            |

| Virtual Component Attributes(VCA) with Formats for Profiling, Selection and Transfer Standard(VCT 2.2.3) | 2       | Virtual Component Transfer<br>DWG       | Revised 2003,3<br>Released 2001,3            |

| Hard Intellectual IP(IP) Tagging Standard                                                                | 2,0     | Intellectual Property<br>Protection DWG | Released 2000,6<br>Revision Released 2006,11 |

| Soft Intellectual Property(IP) Tagging Standard                                                          | 1.0     | Intellectual Property<br>Protection DWG | Released 2004,8<br>Revision Released 2006,11 |

| Virtual Component Interface Standard(OCB 2.2.0)                                                          | 2       | On-Chip Bus DWG                         | Revised 2001.4<br>Released 2000.3            |

### (VSIA의 Technical Documents(2007년 7월 현재))

| Document Name                                                                                      | Version | Authors                                 | Date Issued                         |

|----------------------------------------------------------------------------------------------------|---------|-----------------------------------------|-------------------------------------|

| VSIA Architecture Document                                                                         |         | VSI Alliance                            | Released 1997,3                     |

| VSIA Deliverables Document                                                                         | 2,6,0   | VSI Alliance                            | Revised 2002,5                      |

| Intellectual Property Protection White Paper:<br>Schemes, Alternatives and Discussion(IPPWP 1 1.1) | 1       | Intellectual Property<br>Protection DWG | Revised 2001,1<br>Released 2000,8   |

| White Paper: The Value and Management of Intellectual Assets(IPPWP 2 1.0)                          |         | Intellectual Property<br>Protection DWG | Revised 2002,6<br>Released 2002,6   |

| Technical Measures and Best Practices for<br>Securing Proprietary Information(IPPWP 3 1.0)         | 1.0     | Intellectual Property<br>Protection DWG | Revised 2002,11<br>Released 2002,11 |

| Platform-Based Design Taxonomy Version 1(PBD 11.0)                                                 | _       | Platform-Based Design DWG               | Member review ended 2003,12         |

| VSIA System Level Design Model Taxonomy<br>Document(SLD 2 2.1)                                     | 2       | System-Level Design DWG                 | Released 2001,7                     |

| Taxonomy of Functional Verification for Virtual Component Development and Integration(VER 1 1,2)   | 1       | Functional Verification DWG             | Released 2001,1                     |

| VSIA QIP Metric version 3,1                                                                        | 1,11    |                                         | Released 2004,6                     |

| Hard IP Tag Reader/Writer                                                                          | 1,1     | IP Protection                           | Released 2006,11                    |

| Virtual Component Interface Standard(OCB 2.2.0)                                                    | 2       | On-Chip Bus DWG                         | Revised 2001,4<br>Released 2000,3   |

○ VSIA의 활동 종료 이후 SoC 관련 표준화를 넘겨받은 IEEE DASC는 SoC 기술 전반에 걸쳐서 다양한 활동을 진행하고 있음. IEEE DASC에서 SoC 관련 표준화 활동을 진행하고 있는 Working Group은 다음과 같음

### (IEEE DASC의 Working Group(2008년 8월 현재))

| Project Number | Working Group                                                                                           | Status   |  |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------|----------|--|--|--|--|

| P1076          | Standard VHDL Language Reference Manual                                                                 | Active   |  |  |  |  |

| P1076,1        | P1076,1 Standard VHDL Analog and Mixed-Signal Extensions                                                |          |  |  |  |  |

| P1076.1.1      | 1076,1,1 Standard VHDL Analog and Mixed-Signal Extensions - Packages for Multiple Energy Domain Support |          |  |  |  |  |

| P1076,2        | 076.2 IEEE Standard VHDL Mathematical Packages                                                          |          |  |  |  |  |

| P1076,3        | Standard VHDL Synthesis Packages                                                                        | Inactive |  |  |  |  |

| P1076.4        | Standard VITAL ASIC Modeling Specification                                                              | Active   |  |  |  |  |

| P1076,6        | Standard for VHDL Register Transfer Level Synthesis                                                     | Inactive |  |  |  |  |

| P1164          | Standard Multivalue Logic System for VHDL Model Interoperability                                        | Inactive |  |  |  |  |

| P1364          | Standard for Verilog Hardware Description Language                                                      | Active   |  |  |  |  |

| P1364.1        | Standard for Verilog Register Transfer Level Synthesis                                                  | Inactive |  |  |  |  |

| P1481          | Standard for Integrated Circuit Open Library Architecture                                               |          |  |  |  |  |

| P1497          | 97 Standard for Standard Delay Format for the Electronic Design Process                                 |          |  |  |  |  |

| P1499          | 99 Standard Interface for Hardware Description Models of Electronic Components                          |          |  |  |  |  |

| P1577          | Object Oriented VHDL                                                                                    | Inactive |  |  |  |  |

| P1603          | Standard for an Advanced Library Format Describing Integrated Circuit Technology, Cells, and Blocks     | Inactive |  |  |  |  |

| P1604          | Library IEEE                                                                                            | Inactive |  |  |  |  |

| P1647          | Standard for the Functional Verification Language 'e'                                                   | Active   |  |  |  |  |

| P1666          | Standard System C Language Reference Manual                                                             | Inactive |  |  |  |  |

| P1685          | SPIRIT XML Standard for IP Description                                                                  | Active   |  |  |  |  |

| P1699          | Rosetta System Level Design Language Standard                                                           | Active   |  |  |  |  |

| P1778          | ESTEREL v7 Language Standardization                                                                     | Active   |  |  |  |  |

| P1800          | SystemVerilog: Unified Hardware Design, Specification and Verification Language                         | Active   |  |  |  |  |

| P1801          | Standard for the Design & Verification of Low Power ICs                                                 | Active   |  |  |  |  |

| P1850          | Standard for PSL: Property Specification Language                                                       | Active   |  |  |  |  |

# 2.4. 표준화항목별 현황 분석표

| 표준화                   | 대상항목  | IP 설계 기술                                                                                    | IP 검증 및 테스트 기술                | IP 유통 표준                                                                                                                    | 시스템 통합 기술                     | 시스템 부품 기술                     |  |

|-----------------------|-------|---------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------|--|

| 표준화항목                 |       | - HDL Coding - IP Interface - AMS IP - Platform-Based Design                                | - IP Test/Verification        | – IP 전달물<br>– IP 품질 평가<br>– IP 보호<br>– IP Numbering                                                                         | – Chip-Package<br>Codesign    | - Sensor 부품                   |  |

| 시장현황                  | 국내    | 시장 확립                                                                                       | 시장의 관심도는 높으나<br>시장 자체는 아직 미성숙 | 시장 정립 중                                                                                                                     | 시장의 관심도는 높으나<br>시장 자체는 아직 미성숙 | 시장의 관심도는 높으나<br>시장 자체는 아직 미성숙 |  |

| 및 전망                  | 국외    | 시장 확립                                                                                       | 시장 정립 중                       | 시장 정립 중                                                                                                                     | 시장 정립 중                       | 시장 정립 중                       |  |

| 기술개발<br>현황 및          | 국내    | 본격 응용 기술 연구 중,<br>제품 상용화 중                                                                  | 기초 기술 연구 중                    | 기초 기술 연구 중                                                                                                                  | 기초 기술 연구 중                    | 기초 기술 연구 중                    |  |

| 전왕 및<br>전망            | 국외    | 본격 응용 기술 연구 중,<br>제품 상용화 중                                                                  | 본격 응용 기술 연구 중                 | 본격 응용 기술 연구 중                                                                                                               | 본격 응용 기술 연구 중,<br>제품 상용화 중    | 본격 응용 기술 연구 중,<br>제품 상용화 중    |  |

|                       | 국내    | - HDL Coding: 상용화 - IP Interface: 시제품/프로토타입 - AMS IP: 구현 - Platform-Based Design: 시제품/프로토타입 | 구현                            | <ul> <li>- IP 전달물: 구현</li> <li>- IP 품질평가: 구현</li> <li>- IP 보호:</li> <li>- IM품/프로토타입</li> <li>- IP Numbering: 상용화</li> </ul> | 설계                            | 설계                            |  |

| 기술개발<br><del>수준</del> | 국외    | - HDL Coding: 상용화<br>- IP Interface: 구현<br>- AMS IP: 상용화<br>- Platform-Based<br>Design: 상용화 | 상용화                           | - IP 전달물: 구현<br>- IP 품질평가: 상용화<br>- IP 보호: 구현<br>- IP Numbering: 상용화                                                        | 구현                            | 구현                            |  |

|                       | 기술격차  | 미국-2년                                                                                       | 미국-2년                         | 미국-1년                                                                                                                       | 미국-2년                         | 미국-2년                         |  |

|                       | 관련제품  | 없음                                                                                          | 없음                            | 없음                                                                                                                          | 없음                            | 없음                            |  |

| IPR                   | 국내    | 없음                                                                                          | 없음                            | 없음                                                                                                                          | 없음                            | 없음                            |  |

| 보유현황                  | 국외    | 없음 없음                                                                                       |                               | 없음                                                                                                                          | 없음 없음                         |                               |  |

| IPR확보                 | 가능분야  | 표준 Platform 및 표준<br>AMS                                                                     | 표준 검증 모델                      | IP 보호 체계 및 IP<br>Numbering 체계                                                                                               | 표준 Pin 배치 및 표준<br>Package     | 표준 연결 체계                      |  |

| IPR확보                 | 1 가능성 | - HDL Coding: 보통<br>- IP Interface: 보통<br>- AMS IP: 높음<br>- Platform-Based<br>Design: 높음    | 높음                            | - IP 전달물: 보통<br>- IP 품질평가: 보통<br>- IP 보호: 높음<br>- IP Numbering: 높음                                                          | 높음                            | 보통                            |  |

| 표준화                      | 대상항목                             | IP 설계 기술                                                                                                                        | IP 검증 및 테스트 기술                           | IP 유통 표준                                                                                              | 시스템 통합 기술                    | 시스템 부품 기술                      |  |

|--------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------|--|

| 표준화 현                    | 황 및 전망                           | IP 설계 시장의 활성화를<br>위해서 큰 도움이 됨                                                                                                   | IP 검증 및 테스트 시장<br>의 활성화를 위해서 다소<br>도움이 됨 | IP 유통 시장의 활성화를<br>위해서 반드시 필요                                                                          | SiP 시장의 활성화를 위<br>해서 큰 도움이 됨 | Sensor 시장의 활성화를<br>위해서 큰 도움이 됨 |  |

|                          | 국내 TTA                           |                                                                                                                                 | ТТА ТТА                                  |                                                                                                       | 없음                           | 없음                             |  |

|                          | 국외                               | IEEE DASC, SPIRIT,<br>SI2, ACCELLERA                                                                                            | IEEE DASC, SPIRIT,<br>SI2, ACCELLERA     | IEEE DASC                                                                                             | 없음                           | 없음                             |  |

| 표준화<br>기구/단체             | 국내참여<br>업체 및<br>기관현황             | 삼성, KETI                                                                                                                        | 삼성, KETI                                 | 삼성, KETI 없음                                                                                           |                              | 없음                             |  |

|                          | 국내기여도                            | - HDL Coding: 보통<br>- IP Interface: 보통<br>- AMS IP: 낮음<br>- Platform-Based<br>Design: 낮음                                        | 보통                                       | – IP 전달물: 보통<br>– IP 품질평가: 보통<br>– IP 보호: 보통<br>– IP Numbering: 높음                                    | 보통                           | 垛                              |  |

|                          | 국내                               | - HDL Coding: 표준안<br>최종검토<br>- IP Interface: 표준기획<br>- AMS IP: 표준기획<br>- Platform-Based<br>Design: 표준기획                         | 표준기획                                     | - IP 전달물:<br>표준화 항목승인<br>- IP 폭질평가:<br>표준안 최종검토<br>- IP 보호: 표준기획<br>- IP Numbering:<br>표준 제/개정        | 표준기획                         | 표준기획                           |  |

| 표준화<br>수준                | 국외                               | - HDL Coding: 표준 제<br>/개정<br>- IP Interface: 표준안<br>최종검토<br>- AMS IP: 표준화 항목<br>승인<br>- Platform-Based<br>Design: 표준안 개발/<br>검토 | 표준안 최종검토                                 | - IP 전달물:<br>표준안 개발/검토<br>- IP 품질평가:<br>표준 제/개정<br>- IP 보호:<br>표준안 최종검토<br>- IP Numbering:<br>표준 제/개정 | 표준기획                         | 표준기획                           |  |

| 인프:<br>(시장요 <del>-</del> | L<br>E준화의<br>라수준<br>구정도 및<br>벼도) | - HDL Coding: 보통<br>- IP Interface: 보통<br>- AMS IP: 낮음<br>- Platform-Based<br>Design: 낮음                                        | 낮음                                       | - IP 전달물: 보통<br>- IP 품질평가: 보통<br>- IP 보호: 보통<br>- IP Numbering: 높음                                    | 낮음                           | 낮음                             |  |

# 3. 중점 표준화항목의 표준화 추진전략

### 3.1. 중점기술의 표준화 환경분석

#### 3.1.1. 표준화 추진상의 문제점 및 현안사항

- 가장 많은 표준화 작업이 진행되어온 IEEE DASC, SPIRIT 등의 표준은 강제성을 가지지 않는 사실상의 표준 (De facto standard)이나, 대부분의 기업들이 이들 표준을 권고안으로 반영하고 있기 때문에 국제 표준에 근접 하게 인정받고 있음. 그러나 국내 기업들은 이들 표준화 활동에 매우 소극적인 경향을 보이고 있어서 우리나라 가 표준 경쟁에서 뒤처질 우려가 높음

- 최근 들어 활발하게 표준화 작업을 시작한 SI2와 Accellera의 경우 국내 기업체, 연구소, 대학 등의 참여가 전무한 실정임. 비록 이들 두 기관이 국내에서 그다지 활발하게 발달하지 않은 분야를 다룬다고 하더라도 이들 두 기관에서 제정된 표준은 SoC 설계에서 큰 비중을 차지하는 IP 설계 및 CAD 툴 개발에 적용되기 때문에 국내에서도 이들 두 기관에의 적극적인 참여가 절실히 요구됨

- 국내에 IP/SoC 분야의 설계방법론 등 표준화가 시도되고 있으나, 학계의 연구 활동에 집중되어 있는 실정이 며, 산업계에서는 국내 표준화 활동과 국내 표준의 적용에 많이 관심을 기울이지 않는 실정임. 따라서 국내에서 제정된 표준이 가치를 인정받기 위해서는 산업 현장에서 실제적으로 사용될 수 있는 표준안을 제정하고, 기업들이 제품에 적용함으로써 표준화의 선 순환적 발전을 위해서는 산·학·연의 공동된 컨소시엄 구성이 필요함. 즉, 표준화의 중요성을 인식하고 자발적으로 참여하여 공통된 표준화 사업이 실제적으로 진행될 수 있도록하는 동기부여가 중요함

- 전문가 중에서 IP Interface와 IP 전달물의 경우 개별 기업을 중심으로 독자적인 작업이 상당 부분 진행되고 이들이 이미 일반화되어 표준화에 어려움이 있을 것이라는 의견이 일부 존재함

### 3.1.2. SWOT 분석 및 표준화 추진방향

|                    |                                                                                                                                                                                                                                   |                                                                                                                   |        | 강 점 요 인 (S)                                                    | 약 점 요 인 (W)                                  |                                                                |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------|--|

|                    | 국내역량요인                                                                                                                                                                                                                            |                                                                                                                   |        |                                                                | 시장                                           | - 부품의 해외 의존도가 높음                                               |  |

|                    |                                                                                                                                                                                                                                   |                                                                                                                   | 기<br>술 |                                                                |                                              | - 설계 기술 및 CAD 툴 기술이 상대적으로 취약함                                  |  |

|                    | 국외환경요인                                                                                                                                                                                                                            |                                                                                                                   |        | - 정부의 정책의지가 확고함(TTA 산하 PG407 설립)                               | 표<br>준                                       | - 국내의 기술 표준 작업이 크게 활성화되지 못함                                    |  |

|                    | 지 가 당 - SoC의 최대 수요처인 모바일, 멀티미디 어 산업이 급성장하고 있음 - 아시아 지역이 SoC의 생산과 소비 중심으로 발전하고 있음  기 회 요 인 인 (O)  - 모바일 기술, 멀티미디어 기술의 발전이 지속됨 - 유비쿼터스 기술, 바이오 기술, 나노 기술이 급격히 발전하여 SoC 기술이 융합 기술의 핵심으로 자리 잡기 시작함  - 유통 표준 등 분야에서 국제 표준을 선도할 기회가 도래함 |                                                                                                                   |        | 황분석에 의한 우선순위: 1<br>P 거래 분야에서 쌓아온 실적을 바탕으로 IP 유통<br>분야의 표준을 선도  | 현황분석에 의한 우선순위: 2<br>- 일본, 대만, 중국과 공동으로 표준 제정 |                                                                |  |

| 회                  |                                                                                                                                                                                                                                   |                                                                                                                   |        | Chip-Package Codesign, Sensor 부품 등 새롭게<br>내두되는 기술 분야의 표준을 선도   |                                              |                                                                |  |

|                    |                                                                                                                                                                                                                                   |                                                                                                                   |        | SO전략: 공격적 전략(강점시용-기회활용) <b>SO</b>                              | WC                                           | WO전략: 만회 전략(약점극복-기회활용)                                         |  |

| 위                  | 시장                                                                                                                                                                                                                                | <ul> <li>국내 파운드리 산업의 경쟁력이 둔화됨</li> <li>메모리 시장의 성장률이 둔화됨</li> <li>아시아, 특히 중국의 급성장으로 인하여<br/>국제 경쟁력이 감소함</li> </ul> |        | ST전략: 다각화 전략(강점사용-위협회피) ST                                     | WT                                           | . WT전략: 방어적 전략(약점최소화-위협회피)                                     |  |

| 급<br>요<br>인<br>(T) | 기<br>술                                                                                                                                                                                                                            | - 핵심 기술의 미확보로 인한 기술 중속의<br>우려가 있음                                                                                 | - 1    | 황분석에 의한 우선순위: 4<br>비메모리 분야의 경쟁력을 강화할 수 있는 기술 분야<br>의 표준 제정에 참여 | {                                            | 황분석에 의한 우선순위: 3<br>실질적 표준이라 하더라도 발빠르게 수용 및 적용하<br>셔 기술 종속을 최소화 |  |

|                    | 표<br>준                                                                                                                                                                                                                            | - 기술 표준 작업이 해외에서 주도적으로<br>진행됨                                                                                     |        |                                                                |                                              |                                                                |  |

#### ○ 현황분석을 통한 우선순위: SO → WO → WT → ST

- SO 전략: 국내 역량의 강점과 기회를 활용하기 위해서는 그동안 IP 거래 분야에서 쌓아온 실적을 바탕으로 IP 유통 분야의 표준을 선도하며, 유비쿼터스 기술, 바이오 기술, 나노 기술의 발전으로 인하여 SoC 기술이 새롭게 융합 기술의 핵심으로 자리 잡기 시작한 점을 감안하여 Chip-Package Codesign, Sensor 부품 등 새롭게 대두되는 기술 분야에서 선도적인 역할을 수행함

- WO 전략: 기회를 활용하여 약점을 극복하기 위해서는 국내 파운드리 산업의 경쟁력이 둔화되고 아시아, 특히 중국의 반도체 산업이 급성장하는 점을 감안하여 일본, 대만, 중국과 협력하여 공동으로 표준을 제정함

- WT 전략: 약점을 최소화하고 위협을 회피하기 위해서는 정식 표준이 아닌 실질적 표준이라 하더라도 발빠르게 수용 및 적용하여 기술 종속을 최소화함

- ST 전략: 강점을 활용하여 위협요소를 회피하기 위해서는 비메모리 분야의 경쟁력을 강화할 수 있는 표준 제정에 참여함

- O 표준화 추진방향: SO 전략을 중점 수행하고 WO 전략을 통해 보완

- SoC 분야에서 새롭게 대두되는 융합 기술은 정부의 강력한 지원에 힘입어 SoC 기술을 세계적으로 선도할 좋은 기회이므로 IP 거래 분야에서 쌓아온 실적을 바탕으로 IP 유통 분야의 표준을 선도하며 Chip—Package Codesign, Sensor 부품 등 새롭게 대두되는 기술 분야의 표준을 선도하는 SO 전략을 중점적으로 수행하고, 일본, 대만, 중국과 협력하여 공동으로 표준을 제정하는 WO 전략을 통해 보완함

### 3.1.3. 표준화 추진체계

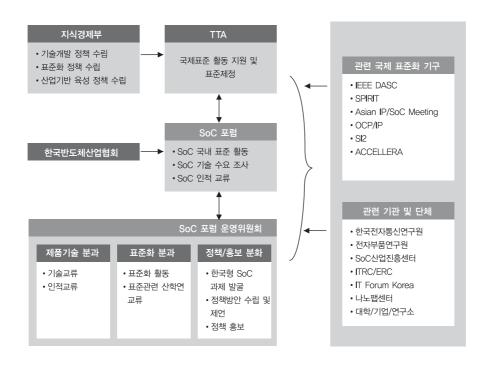

○ 나노 SoC 관련 국내 산·학·연을 중심으로 SoC 포럼을 통하여 국내 표준화 활동을 주도하고, TTA 산하에 구성된 SoC 표준화 전담반(PG407)에서 국내 표준(안)을 개발함. 이를 위해서 SoC 포럼과 TTA PG407을 양대 주축으로 하여 관련 기구. 기관 및 단체와 긴밀한 협조 체제를 구성함

# 3.2. 중점 표준화항목 선정

### 3.2.1. 중점 표준화항목 선정방법

|                   | 전략적 중요도(Priority)     |                                              |           |                                                      |      |                           | 기술적 파급효과(Effect)             |                                           |                                                |                                                |       |                                               |      |

|-------------------|-----------------------|----------------------------------------------|-----------|------------------------------------------------------|------|---------------------------|------------------------------|-------------------------------------------|------------------------------------------------|------------------------------------------------|-------|-----------------------------------------------|------|

|                   | 지(국가 산                | P2<br>공공성(사<br>용자 편리<br>성, 중복<br>투자 방지<br>등) | P3<br>적시성 | P4<br>기술적 선<br>도 가능성<br>(국제표준<br>경쟁력,<br>IPR확보<br>등) |      | PI<br>(Priority<br>Index) | E1<br>기술적 중<br>요도(원천<br>성 등) | E2<br>타 기술에<br>파급효과<br>(연관성,<br>활용성<br>등) | E3<br>시장파급<br>성 및 상<br>용화 가능<br>성(구현가<br>능성 등) | E3<br>시장파급<br>성 및 상<br>용화 가능<br>성(구현가<br>능성 등) | 급효과(산 | E5<br>미래 영향<br>력(미래<br>표준항목<br>에의 적용<br>/응용성) |      |

| 표준화 대상항목          | 평가지표의 중요도             | 0.29                                         | 0.19      | 0.18                                                 | 0.20 | 0.15                      | -                            | 0.22                                      | 0.18                                           | 0.24                                           | 0.25  | 0.12                                          | -    |

|                   | HDL Coding            | 8.87                                         | 9.34      | 6.00                                                 | 7.43 | 9.79                      | 0.83                         | 6.33                                      | 9.53                                           | 6.39                                           | 8,62  | 5.78                                          | 0.74 |

| IP                | IP Interface          | 5.71                                         | 5.97      | 6.00                                                 | 5.00 | 7.81                      | 0.60                         | 6.00                                      | 8.68                                           | 5.10                                           | 5.29  | 6.05                                          | 0.6  |

| 설계기술              | AMS IP                | 5.17                                         | 5.10      | 3.05                                                 | 3.59 | 4.93                      | 0.44                         | 6.39                                      | 4.70                                           | 4.71                                           | 5.72  | 5.34                                          | 0.54 |

|                   | Platform-Based Design | 3.18                                         | 2,78      | 5.04                                                 | 3.90 | 4.34                      | 0.38                         | 5.07                                      | 3.96                                           | 3.31                                           | 3.79  | 3,91                                          | 0.40 |

| IP검증/시험           | IP Test/Verification  | 3.70                                         | 4.00      | 4.81                                                 | 5.17 | 5.32                      | 0.45                         | 5.17                                      | 4.44                                           | 3.34                                           | 3.12  | 3.22                                          | 0.39 |

|                   | IP 전달물                | 5.57                                         | 5.55      | 6.41                                                 | 6.94 | 7.83                      | 0.63                         | 6.32                                      | 5.88                                           | 8.64                                           | 6.09  | 6.79                                          | 0.68 |

| IP유통              | IP 품질평가               | 6.03                                         | 6.05      | 7.39                                                 | 7.01 | 6.61                      | 0.66                         | 4.35                                      | 5.39                                           | 8.68                                           | 6.49  | 6.96                                          | 0.64 |

| Il <del>u s</del> | IP 보호                 | 5.87                                         | 5.74      | 8.28                                                 | 7.36 | 6.43                      | 0.67                         | 5,12                                      | 5.07                                           | 7.66                                           | 6,82  | 7.62                                          | 0.64 |

|                   | IP Numbering          | 4.82                                         | 6.74      | 4.17                                                 | 9.15 | 6.72                      | 0.62                         | 2,31                                      | 2.64                                           | 2,64                                           | 2,27  | 2,73                                          | 0,25 |

| 시스템 통합            | Chip-Package Codesign | 8.79                                         | 8.24      | 8.80                                                 | 7.45 | 4.58                      | 0.78                         | 9.14                                      | 7.94                                           | 6.85                                           | 8,16  | 8.65                                          | 0.81 |

| 시스템 부품            | Sensor 부품             | 8.76                                         | 8.57      | 9.13                                                 | 6.57 | 4.54                      | 0.77                         | 9.30                                      | 7.62                                           | 7.52                                           | 8.72  | 9.36                                          | 0.84 |

| 시스템 무줌            | 초고주파 부품               | 4.76                                         | 3.02      | 2,30                                                 | 2,39 | 2,50                      | 0.32                         | 6.25                                      | 5.42                                           | 6.20                                           | 6.35  | 5.16                                          | 0.60 |

### 3.2.2. 중점 표준화항목 선정사유

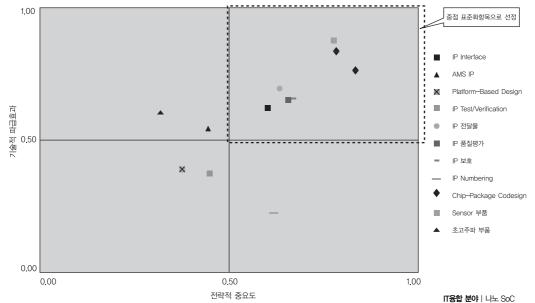

- 전략적 중요도 및 기술적 파급효과의 요소

- 전문가 20인에게 2차에 걸쳐 수행한 설문 조사 결과를 분석하여 12개 표준화 항목의 전략적 중요도(PI)와 기술적 파급 효과(EI)를 결정

- PI와 EI가 1사분면에 위치한 7개 표준화 항목, 즉 HDL Coding, IP Interface, IP 전달물, IP 품질평가, IP 보호, Chip-Package Codesign, Sensor 부품을 중점 표준화 항목으로 선정

### ○ 중점 표준화항목별 선정사유

| 구분        | 중점 표준화 항목                 | 2005년                                              | 2005년                                                                                                                      |

|-----------|---------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| IP 설계     | HDL Coding                | HDL 언어 표준 확장 및 시스템<br>을 기술(description)하는 방법       | HDL 코드를 작성하는 방법에 대한 표준을 제시하여 사용자가 코드에 대한 가독성을<br>통일하고, IP 개발자와 사용자의 설계 도구가 다른 경우에도 동일한 기능의 하드웨어<br>가 설계되도록 하기 위해 매우 중요     |

| IP 설계     | IP Interface              | IP 상호 연결을 위한 연결 방법                                 | 서로 다른 개발자에 의하여 공급되는 IP들을 이용하여 SoC를 설계할 때, IP들이 상호 결합될 수 있도록 Interface를 정의하기 위한 표준이며 IP 개발, 유통 및 재사용시에 매우 중요                |

|           | IP 전달물                    | IP 사용자에게 IP가 전달될 때<br>재사용이 용이하도록 전달해야<br>할 항목      | IP 공급자와 IP 사용자 간의 거래 시에 재사용이 용이하도록 필수적으로 전달하여야할 항목을 정의하는 표준이며 IP 유통 및 재사용 시에 매우 중요                                         |

| IP 유통     | IP 품질 평가                  | IP 사용자가 IP 구매 전에 IP의<br>품질에 대한 정보를 제공하기<br>위한 항목   | IP 사용자가 IP 구매 전 IP의 품질에 대한 정보를 제공하기 위한 항목을 정의하는 표<br>준이며 IP 유통 및 재사용 시에 매우 중요                                              |

|           | IP 보호                     | IP 거래에 있어서, 법적인 IP 보호, 기술적 IP 보호에 대한 방법            | IP 거래 시에 IP의 불법 사용으로부터 IP 공급자를 보호하기 위한 표준이며 IP 유통<br>및 재사용 시에 매우 중요                                                        |

| 시스템<br>통합 | Chip- Package<br>Codesign | 다수의 Chip과 Package를 물<br>리적으로 통합하기 위해 공유<br>해야 할 항목 | 개별 Chip 또는 Die의 형태로 구현된 IP를 물리적으로 통합하여 단일 Package로<br>구현하기 위해 필요한 기술이며 다수의 IP로 구성된 시스템을 실제로 단일 Package<br>내에 통합하기 위해 매우 중요 |

| 시스템<br>부품 | Sensor 부품                 | 다양한 센서 부품 기술 및 시스<br>템에 통합하기 위한 연결 방법              | 물리량, 화학 물질, 전기 신호 등을 감지하는 각종 센서를 설계, 제작하여 시스템에<br>통합하기 위해 필요한 기술이며 BT, NT 기술을 실제로 IT 기술과 통합하여 시스템<br>내부에 구현하기 위해 매우 중요     |

### 3.3. 중점 표준화항목별 세부전략(안)

### 3.3.1. HDL Coding

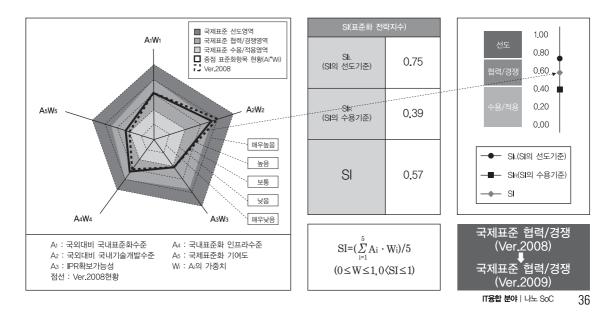

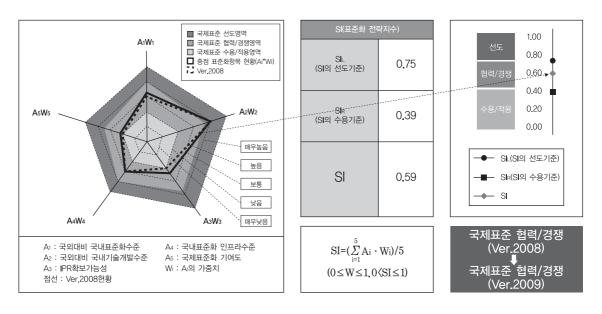

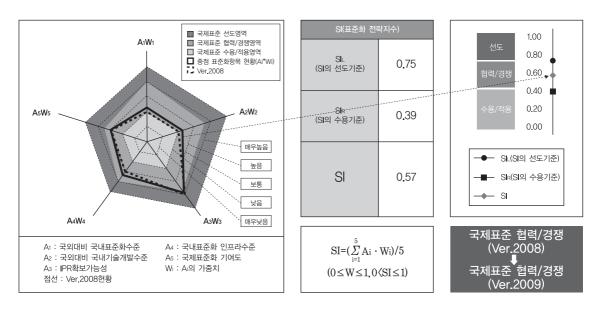

○ 표준상태전이도(표준화 & 기술개발 연계분석)

#### ○ 국제표준화 전략목표 도출

- 국내 산업의 실정에 맞도록 자체 표준안 개발과 아울러 IEEE DASC, SPIRIT, SI2, Accellera 등의 국제 표준을 신속하게 수용하여야 함

- VSIA의 활동을 인계받은 IEEE DASC의 경우, 국내 연구소 및 산업체의 참여가 상당히 미진한 상황임. 따라서 공공성이 강한 국책 연구소의 국제 표준화 활동을 크게 장려할 필요가 있음

- 자체 표준안 개발의 주체인 SoC Forum 및 TTA PG407의 경우 개발 의지가 강력하고 비교적 활발한 활동을 벌이고 있으나 국가적인 재정 및 정책 지원 미비로 인하여 많은 어려움을 겪고 있음. 따라서 SoC Forum 및 TTA PG407에 대한 지원을 시급히 강화해야 함

- HDL Coding의 경우 자체 표준안 제정 작업이 마무리 단계에 들어갔으므로 Revision 2 등의 차기 표준안에 대한 기획을 시작하여야 함

- HDL Coding 분야의 국제 표준안은 대형 CAD 회사를 중심으로 이루어지며, 개발된 국제 표준안은 세계적 인 SoC 설계 흐름을 좌우하고 있음. 이에 반해 국내에서는 CAD 산업이 취약하여 적극적으로 국제 표준안 제정에 참여하거나 자체 표준안을 제정하기에 많은 어려움이 있음. 따라서 국가적으로 진행되고 있는 인력 양성 사업에서 CAD 전문 인력의 양성이 이루어져야 함

- HDL Coding의 경우 국내 기술 개발 수준[A2W2]은 국제 상위 수준에 근접하여 있으나, 표준화에 대한 관심 부족으로 표준화는 상대적으로 늦은 상태임. 표준화 개발과 아울러 산업계와 연구소 등에 국내 표준의 활용 도를 높이기 위한 홍보를 강화해야 함

- HDL Coding의 경우 IPR 확보 가능성[A3W3]과 국제 표준화 기여도[A5W5]는 상대적으로 낮은 수준에 머무름. 따라서 국가적으로 이 부분에 대한 보완 사업을 추진해야 함

- SIPAC 사업이 종료된 후, 후속 사업인 KIPEX 사업에서 표준화 활동의 비중이 작아짐. 따라서 자체 표준안 개발의 주체인 SoC Forum 및 TTA PG407의 지원을 강화하거나 독립된 상설 기구화하는 것이 바람직함

# 3.3.2. IP Interface

# ○ 표준상태전이도(표준화 & 기술개발 연계분석)

- 국내 산업의 실정에 맞도록 자체 표준안 개발과 아울러 IEEE DASC, SPIRIT, SI2, Accellera 등의 국제 표준을 신속하게 수용하여야 함

- VSIA의 활동을 인계받은 IEEE DASC의 경우, 국내 연구소 및 산업체의 참여가 상당히 미진한 상황임. 따라서 공공성이 강한 국책 연구소의 국제 표준화 활동을 크게 장려할 필요가 있음

- 자체 표준안 개발의 주체인 SoC Forum 및 TTA PG407의 경우 개발 의지가 강력하고 비교적 활발한 활동을 벌이고 있으나 국가적인 재정 및 정책 지원 미비로 인하여 많은 어려움을 겪고 있음. 따라서 SoC Forum 및 TTA PG407에 대한 지원을 시급히 강화해야 함

- IP Interface의 경우 Platform-Based Design, IP Test/Verification과 많은 연관 관계를 가지고 있으므로 이들 분야에 대하여 시범 사업을 추진하면서 국제 표준화 활동 및 자체 표준안 제정과 연계하는 것이 바람직함

- IP Interface의 경우 국제 표준화 기여도[A5W5]는 국제 상위 수준에 근접하여 있으나 표준화에 대한 관심 부족으로 표준화는 상대적으로 늦은 상태임. 표준화 개발과 아울러 산업계와 연구소 등에 국내 표준의 활용 도를 높이기 위한 홍보를 강화해야 함

- SIPAC 사업이 종료된 후, 후속 사업인 KIPEX 사업에서 표준화 활동의 비중이 작아짐. 따라서 자체 표준안 개발의 주체인 SoC Forum 및 TTA PG407의 지원을 강화하거나 독립된 상설 기구화하는 것이 바람직함

#### 3.3.3. IP 전달물

# ○ 표준상태전이도(표준화 & 기술개발 연계분석)

- 국내 산업의 실정에 맞도록 자체 표준안 개발과 아울러 IEEE DASC, SPIRIT, SI2, Accellera 등의 국제 표준을 신속하게 수용하여야 함

- VSIA의 활동을 인계받은 IEEE DASC의 경우, 국내 연구소 및 산업체의 참여가 상당히 미진한 상황임. 따라서 공공성이 강한 국책 연구소의 국제 표준화 활동을 크게 장려할 필요가 있음

- 자체 표준안 개발의 주체인 SoC Forum 및 TTA PG407의 경우 개발 의지가 강력하고 비교적 활발한 활동을 벌이고 있으나 국가적인 재정 및 정책 지원 미비로 인하여 많은 어려움을 겪고 있음. 따라서 SoC Forum 및 TTA PG407에 대한 지원을 시급히 강화해야 함

- IP 전달물의 경우 자체 표준안 제정 작업이 상당 부분 진행되어 왔으므로 집중적인 지원을 통하여 자체 표준 안을 확정하고, 이를 바탕으로 Revision 2 등의 차기 표준안에 대한 기획을 시작하여야 함

- IP 전달물의 경우 국내 기술 개발 수준[A2W2]은 국제 상위 수준에 근접하여 있으나, 표준화에 대한 관심 부족으로 표준화는 상대적으로 늦은 상태임. 표준화 개발과 아울러 산업계와 연구소 등에 국내 표준의 활용도를 높이기 위한 홍보를 강화해야 함

- IP 전달물의 경우 IPR 확보 가능성[A3W3]과 국제 표준화 기여도[A5W5]는 상대적으로 낮은 수준에 머무름. 따라서 국가적으로 이 부분에 대한 보완 사업을 추진해야 함

- SIPAC 사업이 종료된 후, 후속 사업인 KIPEX 사업에서 표준화 활동의 비중이 작아짐. 따라서 자체 표준안 개발의 주체인 SoC Forum 및 TTA PG407의 지원을 강화하거나 독립된 상설 기구화하는 것이 바람직함

# 3.3.4. IP 품질평가

# ○ 표준상태전이도(표준화 & 기술개발 연계분석)

- 국내 산업의 실정에 맞도록 자체 표준안 개발과 아울러 IEEE DASC, SPIRIT, SI2, Accellera 등의 국제 표준을 신속하게 수용하여야 함

- VSIA의 활동을 인계받은 IEEE DASC의 경우, 국내 연구소 및 산업체의 참여가 상당히 미진한 상황임. 따라서 공공성이 강한 국책 연구소의 국제 표준화 활동을 크게 장려할 필요가 있음

- 자체 표준안 개발의 주체인 SoC Forum 및 TTA PG407의 경우 개발 의지가 강력하고 비교적 활발한 활동을 벌이고 있으나 국가적인 재정 및 정책 지원 미비로 인하여 많은 어려움을 겪고 있음. 따라서 SoC Forum 및 TTA PG407에 대한 지원을 시급히 강화해야 함

- IP 품질평가의 경우 자체 표준안 제정 작업이 마무리 단계에 들어갔으므로 Revision 2 등의 차기 표준안에 대한 기획을 시작하여야 함

- IP 품질평가의 경우 국내 기술 개발 수준[A2W2]은 국제 상위 수준에 근접하여 있으나, 표준화에 대한 관심 부족으로 표준화는 상대적으로 늦은 상태임. 표준화 개발과 아울러 산업계와 연구소 등에 국내 표준의 활용 도를 높이기 위한 홍보를 강화해야 함

- IP 품질평가의 경우 국내 표준화 기여도[A5W5]는 상대적으로 낮은 수준에 머무름. 따라서 국가적으로 이 부분에 대한 보완 사업을 추진해야 함

- SIPAC 사업이 종료된 후, 후속 사업인 KIPEX 사업에서 표준화 활동의 비중이 작아짐. 따라서 자체 표준안 개발의 주체인 SoC Forum 및 TTA PG407의 지원을 강화하거나 독립된 상설 기구화하는 것이 바람직함

#### 3.3.5. IP 보호

# ○ 표준상태전이도(표준화 & 기술개발 연계분석)

- 국내 산업의 실정에 맞도록 자체 표준안 개발과 아울러 IEEE DASC, SPIRIT, SI2, Accellera 등의 국제 표준을 신속하게 수용하여야 함

- VSIA의 활동을 인계받은 IEEE DASC의 경우, 국내 연구소 및 산업체의 참여가 상당히 미진한 상황임. 따라서 공공성이 강한 국책 연구소의 국제 표준화 활동을 크게 장려할 필요가 있음

- 자체 표준안 개발의 주체인 SoC Forum 및 TTA PG407의 경우 개발 의지가 강력하나 국가적인 재정 및 정책 지원 미비로 인하여 많은 어려움을 겪고 있음. 따라서 SoC Forum 및 TTA PG407에 대한 지원을 시급히 강화해야 함

- IP 보호의 경우 국내 기술 수준이 국제 수준에 비교하여 상당 부분 취약하므로 국내 표준의 개발뿐만 아니라 국제 수준의 수용도 적극적으로 고려하여야 함

- IP 보호의 경우 IPR 확보 가능성[A3W3]은 국제 상위 수준에 근접하여 있으나, 표준화에 대한 관심 부족으로 표준화는 상대적으로 늦은 상태임. 표준화 개발과 아울러 산업계와 연구소 등에 국내 표준의 활용도를 높이기 위한 홍보를 강화해야 함

- IP 보호의 경우 국내 표준화 수준[A1W1]과 국내 기술 개발 수준[A2W2]은 상대적으로 낮은 수준에 머무름. 따라서 국가적으로 이 부분에 대한 보완 사업을 추진해야 함

- SIPAC 사업이 종료된 후, 후속 사업인 KIPEX 사업에서 표준화 활동의 비중이 작아짐. 따라서 자체 표준안 개발의 주체인 SoC Forum 및 TTA PG407의 지원을 강화하거나 독립된 상설 기구화하는 것이 바람직함

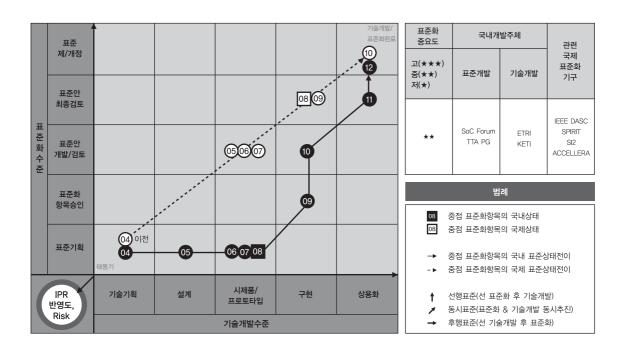

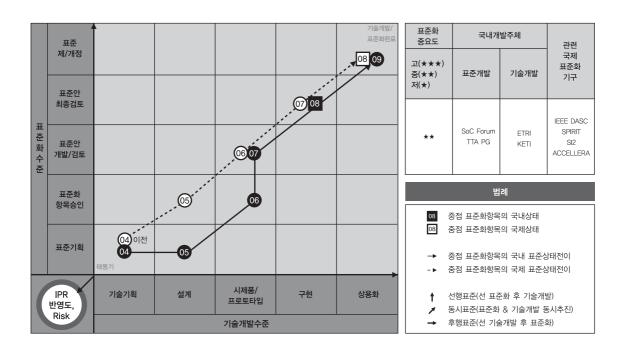

# 3.3.6. Chip-Package Codesign

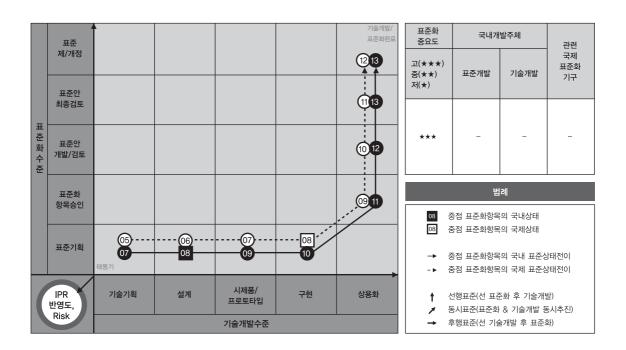

○ 표준상태전이도(표준화 & 기술개발 연계분석)

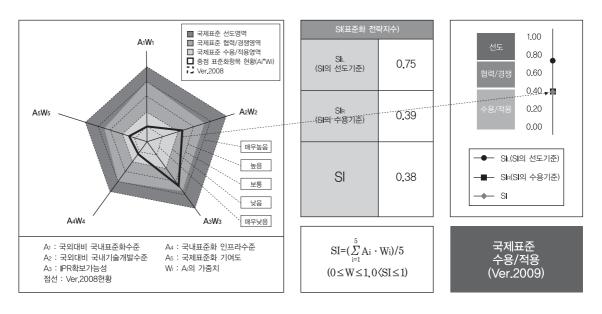

- 최근들어 새로이 각광받기 시작한 기술이며 국제적으로 기술 개발 및 표준화가 크게 진행되고 있지 않으나, 국내의 기술 수준이 국제 수준에 비해 상당히 미흡한 편이므로 SI로 판단하면 수용/적용 전략과 협력/경쟁 전략의 경계에 위치함. Ver.2008에서는 수용/적용 전략에 해당하였으나 Ver.2009에서는 협력/경쟁 전략에 해당하였으므로, 국내 여건이 빠르게 개선되고 있음을 알 수 있음

- 전문가들의 주된 의견에 따르면, Chip-Package Codesign은 상업적으로 파급 효과가 매우 크고 시장 규모 가 큰 편이며 아직까지 국제적인 표준화 작업이 진행되고 있지 않기 때문에 국가적으로 강력한 기술 개발과 함께 적극적인 표준화 작업을 진행하여 국제 표준을 선도하는 것이 유리하다는 결론을 얻음

- 이에 반하여 전문가들의 의견 중에는 국내의 기술 수준이 국제 수준에 비해 상당히 미흡한 편이므로 국제 표준을 수용하는 것이 현실적이라는 의견도 다수 있었음

- 따라서 Chip-Package Codesign의 경우 현 시점에서는 협력/경쟁 전략을 위주로 하되 국제 표준 수용/적용 전략 및 국제 표준 선도 전략에 대해서도 어느 정도 대비하고 있다가 국내의 기술 수준이 발전하는 동향을 지켜보고 국내의 기술 발전 상황이 미흡하면 국제 표준 수용/적용 전략으로 방향 전환하며 국내의 기술 발전 상황이 양호하면 국제 표준 선도 전략으로 방향 전환하는 것이 바람직함

- Chip-Package Codesign의 경우 IPR 확보 가능성[A3W3]은 국제 상위 수준에 근접하여 있으나, 표준화에 대한 관심 부족으로 표준화는 매우 늦은 상태임. 표준화 개발과 아울러 산업계와 연구소 등에 국내 표준의 활용도를 높이기 위한 홍보를 강화해야 함

- Chip-Package Codesign의 경우 국내 표준화 인프라 수준[A4W4]은 매우 낮은 수준에 머무르고 있으며 국 내 표준화 수준[A1W1], 국내 기술 개발 수준[A2W2]과 국제 표준화 기여도[A5W5]도 상대적으로 낮은 수준 에 머무름. 따라서 국가적으로 이 부분에 대한 보완 사업을 추진해야 함

- Chip-Package Codesign의 경우 기술의 특성상 사실상의 표준(De Facto Standard)의 형태가 적합하며, 기술의 상당 부분이 파운드리 업체의 개별 사정과 연관이 있으므로 엄격한 형태의 표준안보다는 유연한 형 태의 가이드라인이 적합하다고 판단됨

- 또한 Chip-Package Codesign의 경우 기술 개발 주체와 표준화 주체가 가능한 일치하는 것이 좋으며, SoC와 타 기술이 융합된 기술이라는 성격을 감안하여 ETRI 등의 국책연구소가 기술 개발 주체와 표준화 주체를 맡는 것도 좋을 것이라고 생각됨

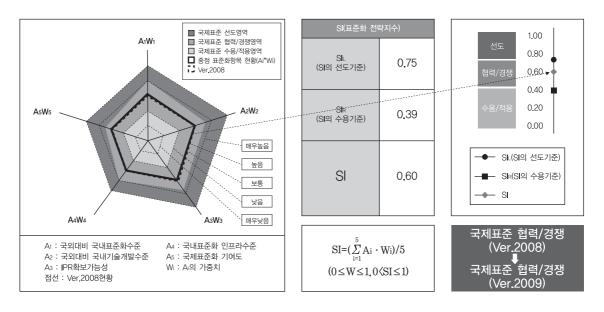

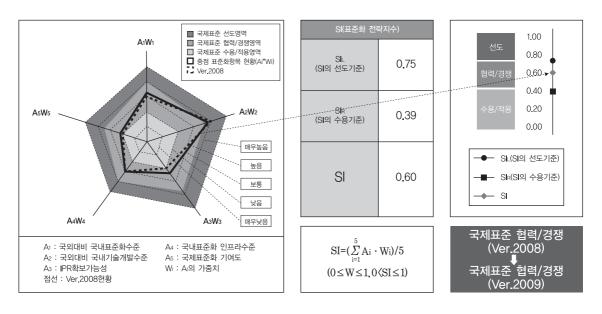

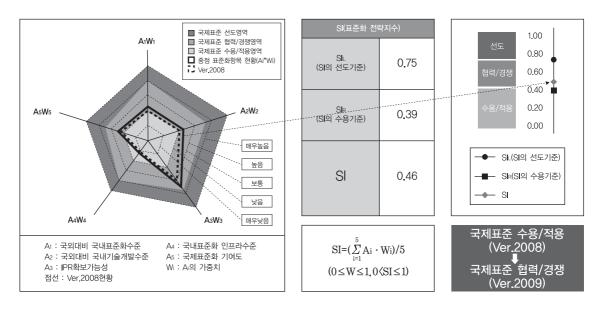

# 3.3.7. Sensor 부품

# ○ 표준상태전이도(표준화 & 기술개발 연계분석)

- 최근들어 새로이 각광받기 시작한 기술이며 국제적으로 기술 개발 및 표준화가 크게 진행되고 있지 않으나, 국내의 기술 수준이 국제 수준에 비해 상당히 미흡한 편이므로 SI로 판단하면 수용/적용 전략과 협력/경쟁 전략의 경계에 위치함, Ver, 2008에서는 포함되지 않았다가 Ver, 2009에서 새로이 추가된 항목임

- 전문가들의 주된 의견에 따르면, 국내의 기술 수준이 국제 수준에 비해 상당히 미흡한 편이므로 국제 표준을 수용하는 것이 현실적이라는 결론을 얻음

- 이에 반하여 전문가들의 의견 중에는 Sensor 부품은 상업적으로 파급 효과가 매우 크고 시장 규모가 큰 편이 며 아직까지 국제적인 표준화 작업이 진행되고 있지 않기 때문에 국가적으로 강력한 기술 개발과 함께 적극적인 표준화 작업을 진행하여 국제 표준을 선도하는 것이 유리하다는 의견도 다수 있었음

- 따라서 Sensor 부품의 경우 현 시점에서는 수용/적용 전략을 위주로 하되 국제 표준 협력/경쟁 전략 및 국제 표준 선도 전략에 대해서도 어느 정도 대비하고 있다가 국내의 기술 수준이 발전하는 동향을 지켜보고 국내 의 기술 발전 상황이 양호하면 국제 표준 협력/경쟁 전략 및 국제 표준 선도 전략으로 방향 전환하는 것이 바람직함

- Sensor 부품의 경우 IPR 확보 가능성[A3W3]은 국제 상위 수준에 근접하여 있으나, 표준화에 대한 관심 부족으로 표준화는 매우 늦은 상태임. 표준화 개발과 아울러 산업계와 연구소 등에 국내 표준의 활용도를 높이기 위한 홍보를 강화해야 함

- Sensor 부품의 경우 국내 표준화 수준[A1W1], 국내 표준화 인프라 수준[A4W4]과 국제 표준화 기여도 [A5W5]이 매우 낮은 수준에 머무르고 있으며 국내 기술 개발 수준[A2W2]도 상대적으로 낮은 수준에 머무름. 따라서 국가적으로 이 부분에 대한 보완 사업을 추진해야 함

- Sensor 부품의 경우 기술의 특성상 사실상의 표준(De Facto Standard)의 형태가 적합하며, 다양한 센서를 단일 프레임워크의 표준안에서 지원하기가 사실상 불가능하므로 엄격한 형태의 표준안보다는 유연한 형태 의 가이드라인이 적합하다고 판단됨

- 또한 Sensor 부품의 경우 기술 개발 주체와 표준화 주체가 가능한 일치하는 것이 좋으며, SoC와 타 기술이 융합된 기술이라는 성격을 감안하여 ETRI 등의 국책연구소가 기술 개발 주체와 표준화 주체를 맡는 것도 좋을 것이라고 생각됨

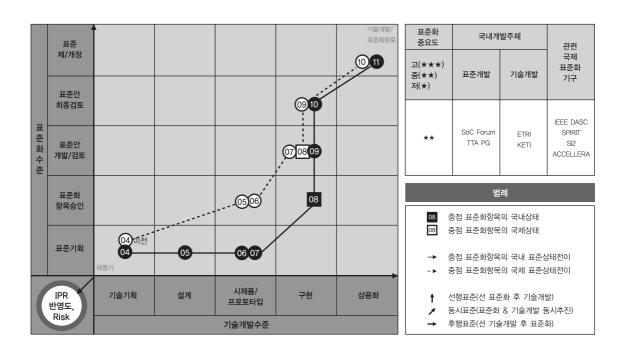

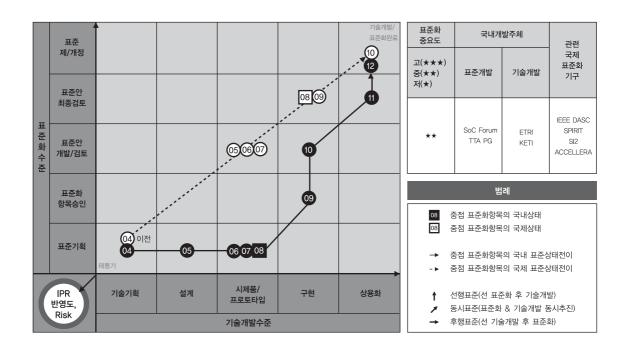

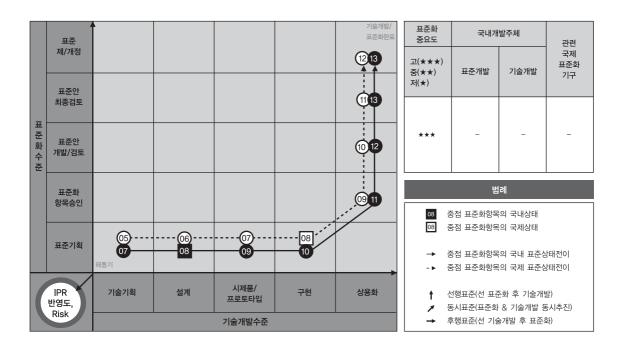

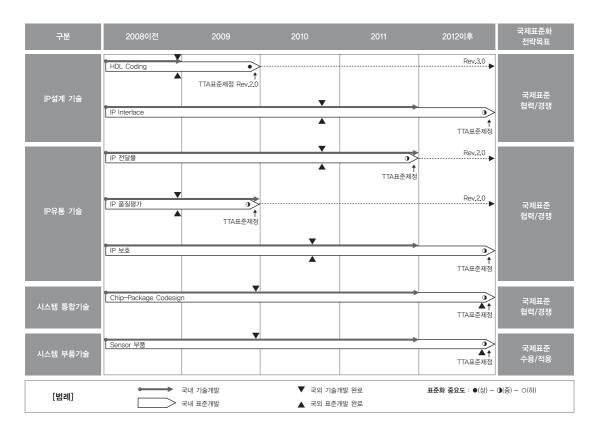

# 3.4. 중장기 표준화로드맵

# 3.4.1. 중기('09~'11) 표준화로드맵

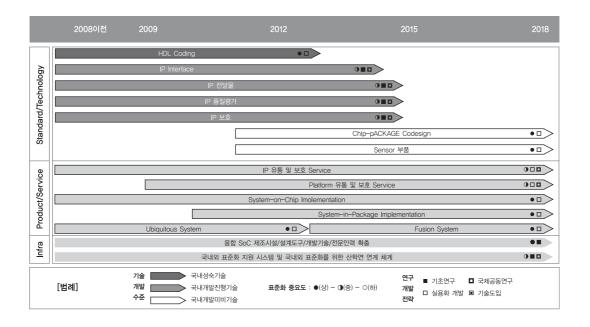

# 3.4.2. 장기 표준화로드맵(10년 기술예측)

# [국내외 관련표준 대응리스트]

| 구분                   | 표준화 항목                       | 표준명                   | 기구(업체) | 제정연도 | 재개정 현황 | 국내 관련표준              | 국내 추진기구   |

|----------------------|------------------------------|-----------------------|--------|------|--------|----------------------|-----------|

| IP 설계<br>기술          | HDL Coding                   | HDL Coding            | VSIA   | 2004 | 초안     | HDL Coding           | SoC Forum |

|                      | IP Interface                 | IP Interface          | VSIA   | 2000 | 제정/개정  | -                    | _         |

|                      | AMS IP                       | AMS IP                | VSIA   | 1999 | 초안     | AMS IP               | SoC Forum |

|                      | Platform<br>Based<br>Design  | Platform-Based Design | VSIA   | 2003 | 초안     | -                    | ETRI      |

| IP 검증<br>및 테스트<br>기술 | IP Test/<br>Verification     | IP Test/Verification  | VSIA   | 2001 | 제정/개정  | IP Test/Verification | SoC Forum |

| IP 유통<br>표준          | IP 전달물                       | IP 전달물                | VSIA   | 2001 | 제정/개정  | IP 전달물               | SoC Forum |

|                      | IP 품질 평가                     | IP 품질 평가              | VSIA   | 2002 | 초안     | IP 품질 평가             | SoC Forum |

|                      | IP 보호                        | P 보호                  | VSIA   | 2000 | 초안     | -                    | _         |

|                      | IP<br>Numbering              | IP 전달물                | _      | _    | _      | IP Numbering         | IT SoC 협회 |

| IP 통합<br>기술          | Chip-<br>Package<br>Codesign | -                     | _      | -    | _      | _                    | _         |

# [참고문헌]

- [1] IT SoC 산업 동향, IT-SoC 협회

- [2] www.vsia.org

- [3] www.si2.org

- [4] www.accellera.org

- [5] www.spiritconsortium.org

- [6] www.socforum.org

- [7] www.kisti.re.kr

- [8] www.itfind.or.kr

- [9] www.ocpip.org

- [10] www.dasc.org

- [11] IT839 전략 기획보고서(5, IT-SoC), 정보통신연구진흥원, 2004년 6월

- [12] IT839 전략 표준화 로드맵 종합보고서, ver.2007, p166-209, 한국정보통신기술협회, 2006년12월

- [13] HDL을 이용한 SoC 및 IP 설계 기법, 강성호외 3인, 홍릉과학출판사, 2004년 4월

- [14] ITRS(International Technology Roadmap for Semiconductors, http://www.itrs.net

- [15] SiP 기술, 주간기술동향, 2006년 4월

- [16] IT839 전략의 차세대 수출 주력 품목 해외 진출 전략 개발, 정보통신연구진흥원, 2006년 9월

# [약어]

AMS Analog Mixed Signal

DTV Digital TV

DASC Design Automation Standards Committee

ETRI Electronics and Telecommunications Research Institute

HDL Hardware Description Language

IEEE Institute of Electrical and Electronics Engineers

IP Intellectual Property

ITRI Industrial Technology Research Institute

IMEC Inter-University Microelectronics Center

KIPEX Korean Semiconductor Intellectual Property Exchange

KETI Korea Electronics Technology Institute

MEMS Micro Electro-Mechanical System

OCP/IP Open Core Protocol International Partnership

SI2 Silicon Integration Initiative

SiP System-in-Package

SPIRIT Structure for Packaging, Integrating, and Reusing IP within Tool Flows

SIPAC System Integration and IP Authoring Center

SoC System-on-Chip

STARC Semiconductor Technology Academic Research Center

TTA Telecommunications Technology Association

TTM Time to Market

VSIA Virtual Socket Interface Alliance